Information and Communication Technologies (ICT) Programme

## Project Nº: H2020-ICT-2016-1-732105

# **D5.1: CERBERO Holistic Methodology** and Integration Interfaces (Final Version)

| Lead Beneficiary:               | AI         |

|---------------------------------|------------|

| Work package:                   | WP5        |

| Date:                           | 28/08/2019 |

| Distribution - Confidentiality: | [Public]   |

**Abstract:** This is an updated report on integration activities with emphasis on cross-layer and cross abstraction levels integration methodology as well as operational interfaces among tools. Here presented is a definition of CERBERO holistic design framework, the

## WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

integration roadmap followed and the interfaces developed. This release of the deliverable is the final of three releases, of which the first D5.4 and D5.5 are already available.

© 2017 CERBERO Consortium, All Rights Reserved.

## Disclaimer

This document may contain material that is copyright of certain CERBERO beneficiaries, and may not be reproduced or copied without permission. All CERBERO consortium partners have agreed to the full publication of this document. The commercial use of any information contained in this document may require a license from the proprietor of that information.

| Num.       | Beneficiary name                                                                | Acronym | Country |

|------------|---------------------------------------------------------------------------------|---------|---------|

| 1 (Coord.) | IBM Israel – Science and Technology LTD                                         | IBM     | IL      |

| 2          | Università degli Studi di Sassari                                               | UniSS   | IT      |

| 3          | Thales Alenia Space Espana, SA                                                  | TASE    | ES      |

| 4          | Università degli Studi di Cagliari                                              | UniCA   | IT      |

| 5          | Institut National des Sciences Appliquees de<br>Rennes                          | INSA    | FR      |

| 6          | Universidad Politecnica de Madrid                                               | UPM     | ES      |

| 7          | Università della Svizzera italiana                                              | USI     | СН      |

| 8          | Abinsula SRL                                                                    | AI      | IT      |

| 9          | Ambisense LTD                                                                   | AS      | UK      |

| 10         | Nederlandse Organisatie Voor Toegepast<br>Natuurwetenschappelijk Ondeerzoek TNO | TNO     | NL      |

| 11         | Science and Technology                                                          | S&T     | NL      |

| 12         | Centro Ricerche FIAT                                                            | CRF     | IT      |

The CERBERO Consortium is the following:

For the CERBERO Consortium, please see the http://cerbero-h2020.eu web-site.

Except as otherwise expressly provided, the information in this document is provided by CERBERO to members "as is" without warranty of any kind, expressed, implied or statutory, including but not limited to any implied warranties of merchantability, fitness for a particular purpose and non-infringement of third party's rights.

CERBERO shall not be liable for any direct, indirect, incidental, special or consequential damages of any kind or nature whatsoever (including, without limitation, any damages arising from loss of use or lost business, revenue, profits, data or goodwill) arising in connection with any infringement claims by third parties or the specification, whether in an action in contract, tort, strict liability, negligence, or any other theory, even if advised of the possibility of such damages.

The technology disclosed herein may be protected by one or more patents, copyrights, trademarks and/or trade secrets owned by or licensed to CERBERO Partners. The partners reserve all rights with respect to such technology and related materials. Any use of the protected technology and related material beyond the terms of the License without the prior written consent of CERBERO is prohibited.

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

## **Document Authors**

The following list of authors reflects the major contribution to the writing of the document.

| Name(s)               | Organization Acronym |

|-----------------------|----------------------|

| Maria Katiuscia Zedda | AI                   |

| Giuseppe Meloni       | AI                   |

| Michael Masin         | IBM                  |

| Evgeny Shindin        | IBM                  |

| Francesca Palumbo     | UNISS                |

| Karol Desnos          | INSA                 |

| Julio Oliveira        | TNO                  |

| Luca Pulina           | UNISS                |

| Claudio Rubattu       | INSA/UNISS           |

| Tiziana Fanni         | UNICA                |

| Daniel Madroñal       | UPM                  |

| Alfonso Rodriguez     | UPM                  |

| Leonardo Suriano      | UPM                  |

| Rafael Zamacola       | UPM                  |

The list of authors does not imply any claim of ownership on the Intellectual Properties described in this document. The authors and the publishers make no expressed or implied warranty of any kind and assume no responsibilities for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information contained in this document.

| Date       | Ver. | Contributor (Beneficiary) | Summary of main changes                                                                      |

|------------|------|---------------------------|----------------------------------------------------------------------------------------------|

| 01/07/2019 | V0.1 | AI                        | First draft                                                                                  |

| 08/07/2019 | V0.2 | UNICA, UNISS and UPM      | Updated PAPIFY-MDC section,<br>added Spider-PAPIFY-MDC<br>section                            |

| 09/07/2019 | V0.2 | AI and UPM                | New structure with more direct<br>connections included and<br>connection with external tools |

| 15/07/2019 | V0.3 | UPM                       | New sections                                                                                 |

## **Document Revision History**

| 23/07/2019 | V0.4 | IBM       | Refactoring of sections 4 and 5 related to CIF, new structure and content. |

|------------|------|-----------|----------------------------------------------------------------------------|

| 25/07/2019 | V1.0 | AI, UNISS | Review                                                                     |

| 26/07/2019 | V1.1 | UPM       | Fix Section 6                                                              |

| 29/07/2019 | V1.2 | AI        | Refactoring of section 7                                                   |

# WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

## **Table of Contents**

| 1. Exe  | ecutive Summary                                                        | 7    |

|---------|------------------------------------------------------------------------|------|

| 1.1.    | Structure of Document                                                  | 7    |

| 1.2.    | Related Documents                                                      | 7    |

| 1.3.    | Related CERBERO Requirements                                           | 8    |

| 2. Int  | roduction                                                              | 9    |

| 2.1.    | Modelling for Systems Engineering                                      | 9    |

| 2.2.    | Systems Integration from CERBERO Perspective                           | 10   |

| 3. Sta  | te of the Art                                                          | 12   |

| 3.1.    | Usage of Formal Semantics                                              | . 12 |

| 3.2.    | Viewpoint Modelling                                                    | . 13 |

| 3.3.    | MARTE and PiSDF                                                        | 13   |

| 4. CE   | RBERO Integration Methodology                                          | 15   |

| 4.1.    | Tool Suite                                                             |      |

| 4.2.    | System Design and Operational Framework                                | .15  |

| 4.3.    | Simplified Ontology-based Integration with Intermediate Representation |      |

| 4.4.    | Mapping KPIs to Model                                                  |      |

| 4.5.    | OS Qualified as a Toolchain Host                                       | .25  |

| 5. Inte | ernal Interfaces                                                       | 26   |

| 5.1.    | Low-Level Instance Base Interface                                      | .26  |

| 5.2.    | Ontology and Class Definition Interface                                | .27  |

| 5.3.    | Class Base Interface for Directly-Connected Tools.                     |      |

| 5.4.    | Data Serialization and Data Interfaces                                 |      |

| 5.5.    | Ontology Alignment and Equivalence Rules                               | .33  |

| 6. Dir  | ect Tool Integration Holistic Methodology                              | 36   |

| 6.1.    | Integrating PREESM and SPIDER with MDC                                 |      |

| 6.2.    | Integrating PAPIFY with MDC                                            |      |

| 6.3.    | Integrating SAGE-ReqV and DYNAA                                        |      |

| 6.4.    | Integrating PAPIFY with ARTICO <sup>3</sup>                            |      |

| 6.5.    | Integrating IMPRESS with ARTICo <sup>3</sup>                           |      |

| 6.6.    | Integration ARTICo <sup>3</sup> with PREESM                            | .47  |

| 6.7.    | Integrating Spider with PAPIFY and with MDC                            | . 50 |

| 6.8.    | Integrating ARTICo <sup>3</sup> and MDC with PAPIFY                    |      |

| 6.9.    | Integrating CERBERO Tools with External Tools                          |      |

| 7. Cor  | nclusion                                                               | 54   |

| 7.1.    | Lesson Learned                                                         | . 54 |

| 7.2.    | Operational Objectives Deliverable Contribution                        |      |

| 8. Ref  | erences                                                                | 57   |

## 1. Executive Summary

This is the final version of the integration activities and complete framework characteristics with emphasis on interfaces among tools.

After the first release, D5.4, that has defined CERBERO methodology, following the iterative development scheme of the project, during the Phase II the methodology has been deeply revised, according to possible technical requirements updates, and the verification and fine tuning of the integration process, these updates have been reported in the second version of the deliverable D5.5. Final reporting on integration activities and the complete framework characteristics and interfaces are included in the present deliverable D5.1. Please note that this non-chronological numbering of the deliverable is due to a recent amendment.

In order to speed up and ease the reading and review process the text of sections and paragraphs that have NOT been significantly updated and revised are in dark gray. Sections that have been deeply updated and revised are 4.2, 4.3, 4.4, 5 and 6. Furthermore, a new section 7 has been added.

## **1.1. Structure of Document**

The document starts by an introduction to modeling of CPSs and vision of CERBERO integration. Then state of the art methodologies are reported. Then the report discusses CERBERO design framework integration approach with required interfaces between the myriad of tools across all layers of the toolchain (model, system of system design and analysis and computational level design and implementation). This last part is devoted to explaining the methodological approach related to the tool integration reporting also a number of successful integration endeavors already achieved by the consortium members. The last section summarized the lesson learned during the integration process, and the contribution of the present deliverable to achieve CERBERO operational objectives.

## **1.2. Related Documents**

- D2.2: CERBERO Technical Requirement

- The activities behind D5.5 contribute to satisfying the requirements 0011 and 0012 listed in D2.2.

- D5.4 D5.5: CERBERO Holistic Methodology and Integration Interfaces

- The proposed holistic methodology reported in the D5.4 and D5.5 has been the basis of the D5.1

- D5.2 D5.2: CERBERO Framework Components

- The deliverable reports the component/features of CERBERO design environment that have been integrated

- D5.7: CERBERO Framework Demo

- After phase II, the verification of the proposed process has allowed identifying the correct methodology for the framework integration and to define the semantic integration approach based on CIF (CERBERO Interoperability Framework).

## **1.3.** Related CERBERO Requirements

Deliverable D2.2 of the CERBERO project defines a list of CERBERO Technical Requirements (CTRs) the project should achieve. Each of them is referenced with a unique identifier ranging from 0001 to 0020.

The CERBERO holistic methodology described in the current document address 4 CTRs, as described in the Table 1-1. It is important to note that most of the requirements related to this deliverable are covered by the tools integrated in the framework and are not reported in the following table.

| CTR id | CTR Description                                                                                                                                       | Link with the D5.1 document on CERBERO holistic methodology and integration interfaces                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0001   | CERBERO<br>framework/technology<br>SHOULD increase the level of<br>abstraction at least by one for<br>HW/SW co-design and for<br>System Level Design. | Users can benefit from the integration of lower level HW-<br>development oriented tools with higher abstraction level<br>ones. The entry point for custom accelerators developments<br>are mainly high level dataflow specifications.                                                                                                                                                                                                                                                         |

| 0002   | CERBEROframeworkSHOULDprovideinteroperabilitybetween cross-layer tools and semantics at thesame level of abstraction.                                 | The semantic integration at the same level of abstraction<br>and the interoperability between cross-layer tool has been<br>achieved with the definition and development of CIF.                                                                                                                                                                                                                                                                                                               |

| 0003   | CERBERO<br>framework/technology<br>SHOULD provide incremental<br>prototyping capabilities for<br>HW/SW co-design.                                     | Direct integration of computing level development tools<br>allowed the possibility to complementary and<br>incrementally integrate/assess new features on the systems.<br>Staring from pure SW implementation monitoring<br>capabilities allows to understand what can/should be<br>moved to HW. Different versions of this latter can be<br>customized with a small user effort and time having the<br>same C code as an entry point, leading to a new set of<br>prototypes to be evaluated. |

| 0009   | CERBERO SHALL develop<br>integration methodology and<br>framework.                                                                                    | All the integration related activities, both direct and CIF-<br>based, concurs to the final development of the framework.                                                                                                                                                                                                                                                                                                                                                                     |

Table 1-1: List of CTR addressed by the D5.1

## 2. Introduction

Cyber-Physical Systems (CPS) are engineered systems comprising interacting physical and computational components. In CPS, computation and communication are deeply embedded in and interacting with physical processes to add new capabilities and characteristics to physical systems.

In this report, we investigate how the various system components could be integrated into a holistic operational framework respecting the requirements imposed by the overall system and seeking a new foundation for CPS design, integration and operation. The goal of the project is to deliver a model-based, heterogeneous and robust solution that is going to be customizable (upon scenario needs) and generalizable (to different scenarios).

## 2.1. Modelling for Systems Engineering

Systems Engineering (SE) dictates the design process associated with the development of large-scale products through defining systems and subsystems requirements, their architecture, and critical parameters. With the recent increase in product complexity and business competition, mere intuition of system design engineers has proven insufficient for finding feasible, safe, reliable and affordable designs [1]. Hence modelling started to emerge to overcome these shortcomings and provide a well-thought-out plan for a solid design and smooth implementation and refinement.

In the context of systems engineering, models are created to deal with complexity. In doing so they allow us to understand an area of interest or concern and provide unambiguous communication amongst interested parties, models are leveraged in nearly all stages of the development process. During analysis, models provide an abstract representation of the desired solution, e.g. in terms of dynamic behaviour diagrams such as sequence diagrams and state machines. In the design phase, the software architecture could be abstracted through UML (Unified Modeling Language) component structure diagrams and class diagrams. In addition, ports and interfaces facilitate modelling of data flows between components. From these models, code can be partially generated in the implementation phase. Moreover, many models can be used at several levels of specification of the system. For example, Finite State Machines are useful at the system, and component levels, both for HW and SW. For testing purposes, models are used to generate test cases. To sum it up, Model-Based Systems Engineering (MBSE) or, more generically, Model-Driven Engineering (MDE) has models as the primary data source. Model Driven Development uses the activities associated with modelling to drive the whole development process [2].

From that perspective, specialized modelling tools come into play to increase productivity. There is a plethora of modelling languages such as SysML (a UML extension), AADL (Architecture Analysis & Design Language), and modeling tools such as Excel, IBM Rhapsody, PTC Artisan Studio, Sparx Enterprise Architect, domain-specific tools (e.g. medical, avionics, automotive, marine, space, etc.), and simulation environments such as Simulink and Modelica [1]. The Functional Mock-up Interface (FMI) standard facilitates the exchange of simulation models between suppliers and OEMs. FMI adopts a tool-independent approach for both model exchange and co-simulation of dynamic models

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

using a combination of XML-files and compiled C-code [3]. Its success could be attributed, at least partially, to a minimalistic API allowing high flexibility for tool providers.

There are also black-box integration tools that help with reducing complexity, improving efficiency and cutting development time. FRONTIER - by ESTECO - provides an innovative optimization environment with modular, profiled-based access. ESTECO's integration platform for multi-objective and multi-disciplinary optimization offers a seamless coupling with third party engineering tools, enables the automation of the design simulation process and facilitates analytic decision making. ModelCenter Integrate - by Phonix Integration - allows users to automate any modelling and simulation tool from any vendor, integrate these tools together to create repeatable simulation workflows, set simulation parameters, and automatically execute the workflow. Hence ModelCenter Integrate increases productivity by enabling users to execute significantly more simulations with less time and resources.

The benefits of using models in systems engineering are manifold: Building models is usually easier than building the actual system as a whole from the ground up. Modelling helps to capture, structure, and understand the system and to reveal, early enough, possible problems and potential bugs lurking at every stage of the system design and implementation. It has proven more appropriate for high-stakes and increasingly complex applications such as reconfigurable and adaptive cyber physical systems. Last but not least, integration per se is not a scientific activity, it is rather an engineering problem full of accidental issues (i.e. tools adopting different languages, running on different platforms, vendor-specific components, etc.) CERBERO is no exception; therefore, we decided to adopt a model-based, semantically oriented, approach.

## **2.2.** Systems Integration from CERBERO Perspective

Systems integration is a process whereby a cohesive system is created from components that were not specifically designed to work together. Components of an integrated system are often systems in their own right and integration aims at interconnecting these components together in a layered fashion in order to provide a useful exchange of information, data and/or control between these sub-systems and assuring that the integrated system meets requirements and performs according to user expectations.

To facilitate systems interconnection, an interface is defined and created as a point of interaction between communicating systems. Interfacing may also mean using a common message format, or intermediate representation, to provide kind of a unified communication paradigm across the system entirely, or partially. The translation would be required from the interface of one component to the intermediate representation, or vice versa.

Generally, integration is done considering subsystems as black-boxes, hence creating a middleware to "glue" together these disparate subsystems without them needing to know anything about each other. We support the "open world" assumption, where each tool should assume that all objects may have more properties than it knows about. Inspired by FMI standard, we are developing as simple formalism as possible to exchange objects with properties that tools recognize with middleware support for simple property mappings when it is semantically clear.

## WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

A recommended integration process adopts an iterative – that is, continuous or constantly evolving - integration model rather than a static or fixed model. Hence, it is essential to create a holistic and customizable framework for subsystem integration as these subsystems and tools undergo continuous development. For tracking of integration progress, the integrated system must be verified and validated periodically against system and user requirements toward a mature integration framework for the overall platform or toolchain.

## 3. State of the Art

Systems Engineering governs the design process associated with the development of largescale products through defining systems and subsystems requirements, their architecture, and critical parameters. The recent increase in product complexity and business competition dictates the necessity for finding feasible, safe, reliable and affordable designs. Consequently, three techniques have become popular in helping handle the complexity: layering design process into several levels of abstraction, separation of concerns, and using computerized tools for automation of modelling, optimization and analysis.

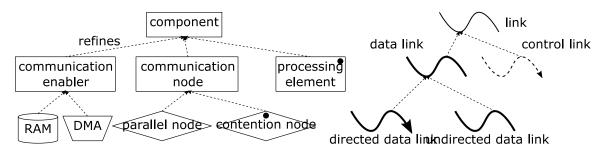

Embedded systems are commonly subject to data intensive processing applications where huge amounts of data are handled in a regular way by means of repetitive computations. These applications deal with intensive or massive parallelism either on the data level or on the task level. High-level analysis of data-intensive applications becomes a complex task necessitating a refinement step toward low levels of abstraction specifying both computation and communication costs in the system.

The following works address the challenge of abstracting system design in a layered fashion that maintains computation and communication specifications of the system and facilitates analysis and optimization hence provides a competitive business edge for the end cyber-physical system.

## **3.1. Usage of Formal Semantics**

Model-Based Engineering of Cyber-Physical Systems needs correct-by-construction design methodologies, hence CPS specification languages require mathematically rigorous, unambiguous, and sound specifications of their syntax and corresponding model semantics. Cyber-physical systems are software-integrated physical systems often used in safety-critical and mission-critical applications, for example in automotive, avionics, chemical plants, or medical applications. In these applications sound, unambiguous and formally specified modelling languages can help developing reliable and correct solutions. Traditional systems engineering is based on causal modelling (e.g., Simulink), in which components are functional and a well-defined causal dependency exists between the inputs and outputs. It is known that such a causal modelling paradigm is imperfect for physical systems and CPS modelling since physical laws are inherently acausal.

Recently, acausal modelling has gained traction and several languages have been introduced for acausal modelling (e.g., Modelica, bond graphs) [4]. Every time a new specification language is introduced, there is a natural demand to extend it to support as many features as possible. Unfortunately, this often leads to enormously large and generic languages, which have many interpretations and variants without a clear, unambiguous semantics. Because of the size of these languages, there is not much hope for the complete formalization of their semantics.

A fundamental problem is that generic languages provide support for many more features than a specific problem needs, still, they often lack support for some essential functions that would be otherwise needed. Thus, in most cases, it is more feasible to use Domain

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

Specific Modeling Languages (DSML) [5] [6], which are designed to support exactly the necessary functions. Additionally, because DSMLs are usually significantly smaller than generic languages, their formal specification is feasible.

The work in [7] discusses the challenges to develop the formal semantics of a CPS-specific modelling language called Cyber-Physical Modeling Language (CyPhyML). The paper formalizes the structural semantics of CyPhyML by means of constraint rules, and the behavioural semantics by defining a semantic mapping to a language for differential algebraic equations. The specification language is based on an executable subset of first-order logic, which facilitates model conformance checking, model checking and model synthesis.

## **3.2. Viewpoint Modelling**

Viewpoint modelling is an effective approach for analyzing and designing complex systems. Splitting various elements and corresponding constraints into different perspectives of interests enables separation of concerns such as domains of expertise, levels of abstraction, and stages in the lifecycle. Specifically, in Systems Engineering different viewpoints could include functional requirements, physical architecture, safety, geometry, timing, scenarios, etc. The first development and refinement step are referred to as Engineering Modeling, and the second optimization and analysis step is referred to as Design Space Exploration (DSE). Consequentially, there are no automatic tools for holistic DSE based on libraries of previously developed and tested Analysis Viewpoints.

Despite partial inter-dependences, models are usually developed independently by different parties, using different tools and languages. However, the essence of Systems Engineering requires repetitive integration of many viewpoints in order to find feasible designs and to make good architectural decisions, e.g., in each mapping between consecutive levels of abstraction and in each design space exploration. This integration into one consistent model becomes a significant challenge from both modelling and information management perspectives.

The work in [1] suggests: (1) a unique modular algebraic viewpoint representation robust to design evolution and suitable for the generation of the integrated optimization/analysis models, and (2) an underlying ontology-based approach for consistent integration of local viewpoint concepts into the unified design space model. The paper shows also an example of an optimization model with different combinations of partially interdependent Analysis Viewpoints. Using the proposed modelling and information management approach the underlying viewpoints' equations can be applied without modification, making the approach pluggable.

## **3.3. MARTE and PiSDF**

At the present time, embedded systems are commonly dedicated to data-intensive processing applications where huge amounts of data are handled in a regular way by means of repetitive computations. These applications deal with intensive or massive parallelism.

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

Indeed, parallel applications can implement two levels of parallelism: data parallelism and task parallelism. High-level analysis of data-intensive applications becomes a complex task necessitating a refinement step toward low levels of abstraction specifying both computation and communication costs in the system. Accurate performance numbers can be reached at the cost of very detailed modelling. On the other hand, a moderate effort for modelling leads to a high-level evaluation task, but the accuracy is lost.

The work in [8] proposes a new approach that takes advantage of Model-Driven Engineering (MDE) foundations and Modeling and Analysis of Real-Time and Embedded Systems (MARTE) profile. The paper defines a transformation to a new level of abstraction that alleviates the exploration and analysis tasks of real-time data-intensive processing applications. This level is based on a novel extension of the famous Synchronous Data Flow (SDF) Model-of-Computation (MoC), the Parameterized and Interfaced Synchronous Dataflow (PiSDF) model. PiSDF facilitates the specification, and especially the analysis of data-intensive applications as it gathers a lot of features including hierarchy, configurability and dynamism. This MoC introduces analysis techniques facilitating the design space exploration task. Then, a high-level analysis of the data-parallel application is performed using the PREESM rapid prototyping tool.

## 4. CERBERO Integration Methodology

## 4.1. Tool Suite

As a first step toward building CERBERO toolchain, IBM and AI in collaboration with the entire consortium have surveyed and agreed upon an array of tools that are either state-of-the-art or already exist within the consortium as fully mature technologies. This survey helped to collect and consolidate information about the functionality of each tool, setup requirements, documentation availability, maturity/readiness level, licensing, and usability domains, and would serve as a reference point for integration efforts. These tools cover the entire stack of a CPS: system model layer, application layer, OS or runtime layer, and hardware abstraction layer. This survey analysis has been the basis for defining a feasible CERBERO integration plan and to specify the interfaces for newly designed tools.

## 4.2. System Design and Operational Framework

For the model-based design of complex systems, such as CPS and CPSoS, a structured and well-defined design framework is essential to guarantee high-quality products that fulfil all requirements of the stakeholders and to enable handling the complexity of such systems by introducing different viewpoints or abstraction layers to model the system under development. Therefore, an important step to obtain a system implementation is the Design Space Exploration (DSE), where design decisions are taken based on goals and requirements defined in previous phases. The set of valid solutions may be restricted by constraints, which could be derived from previously defined requirements considering aspects such as functional requirements, physical architecture, safety, geometry, timing, etc. Valid solutions are rated with respect to defined goals to facilitate a decision toward the choice of final system implementation. Based on this abstract framework, concrete DSE methods can be implemented addressing different kinds of DSE problems that are relevant in industrial practice. In the CERBERO framework we intend to carry out DSE at different levels, at the system level to define the proper distribution among computing nodes, and within the single node to identify the optimal HW/SW partitioning and components set-up. The selected optimal design resulted from the system level DSE should be available (i.e., machine-readable) for HW/SW co-design to define, partially, its functional requirements.

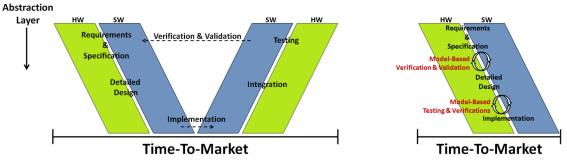

CERBERO design framework aims at shifting designers' work at a higher abstraction level and earlier in the design process, relieving them from manual and complex HW/SW tuning phases. It creates and promotes model-based cross-layer optimization, design, verification and simulation methods that aim at deeply modifying CPS system design approach, shifting from a V model paradigm to a ladder model paradigm, see Figure 4.1, thus slashing the time to market. In the model-based approach, all the properties and system characteristics are tackled concurrently right at the model level at design-time to allow the crossoptimization of physical components, as well as the cross-configuration of the HW and SW layers. Dealing with CPS and CPSoS poses challenges for the overall system assessment (dimensioning and characterizing communication channels, profiling power consumption,

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

etc.) To cope with these challenges, CERBERO features adequate analysis tools and provide sufficient breakdown of all related layers of the system model to guarantee continuous validation.

Figure 4.1: V-Model vs. Ladder System Design Approach

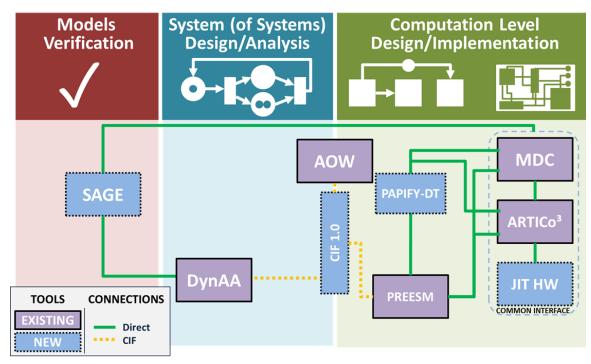

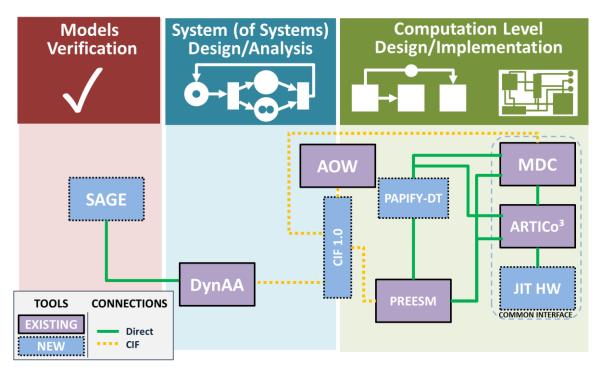

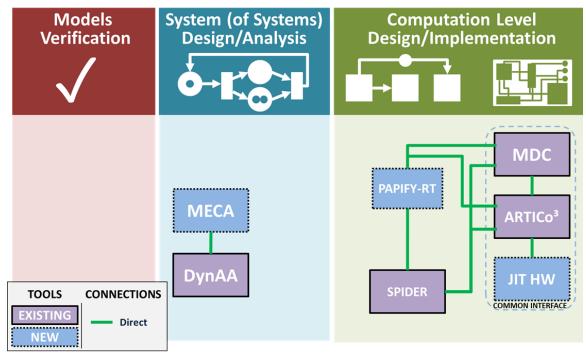

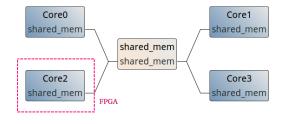

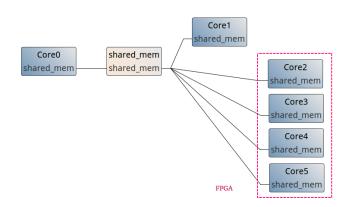

The CERBERO toolchain operates at different levels of abstraction, going from the computation level to the system (of systems) level, delivering also user-level features (i.e. requirements/model verification). Figure 4.3 illustrates the CERBERO tools that offer support at Design-Time as foreseen at M27:

- At Model/Verification Level SAGE suite leverages on formal methods to automatically check the consistency of a set of requirements provided by the user.

- At System (and System of Systems) Level, AOW solves optimization problems to return frontier of Pareto optimal solutions, while DynAA is based on discrete-component models and the related parallelism and physical aspects, finding optimal solutions by means of model simulations.

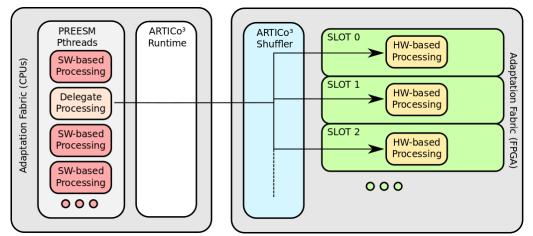

- At the Computation Level several tools, for design implementation, are present.

- PREESM enables parallel-application development with design-time prediction, as well as code generation and re-use capabilities.

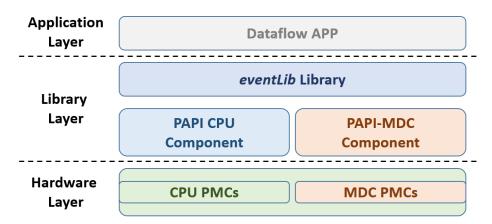

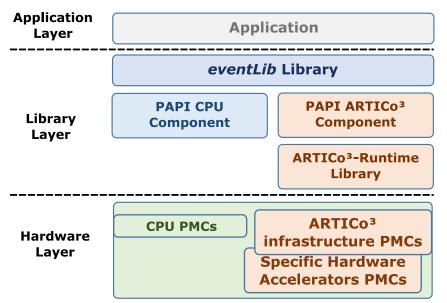

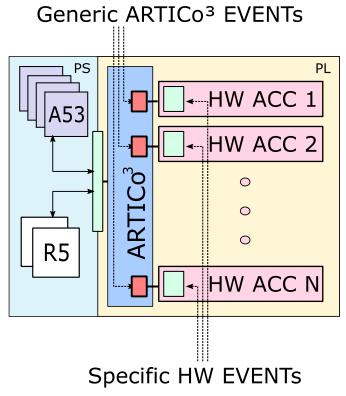

- PAPIFY provides monitoring capabilities by means of an event library aimed at generalizing Performance API (PAPI) for heterogeneous architectures.

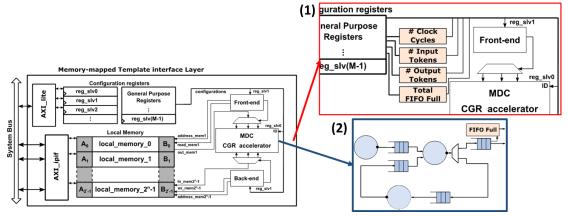

- MDC is an automated dataflow-to-hardware framework for the generation of coarse-grain reconfigurable accelerators.

- ARTICo<sup>3</sup> exploits a DPR-enabled multi-accelerator computing scheme, going to the user-defined application down to the system implementation.

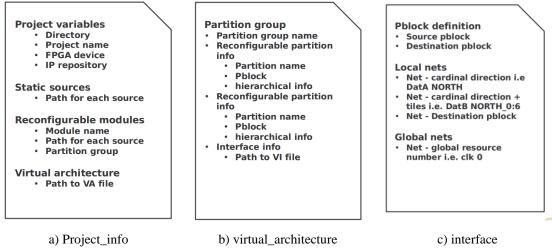

- JIT hardware composition refers to the ability to implement, at run-time, hardware accelerators on FPGAs without a pre-synthesized design. IMPRESS, belonging to the JIT HW design suite, is a TCL script-based tool for the automated generation of relocatable partial bitstreams under Vivado.

At design-time, using intermediate semantics for integration through the CERBERO Integration Framework (CIF) has allowed requirements analysis and verification at the model level. Integration of some tools at the computational level (both for SW and HW design), however, is more implementation oriented since interfaces between these tools

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

have already been coded or currently being developed and tested in a DIRECT INTEGRATION tool-to-tool manner. In Figure 4.2 and Figure 4.3 connection achieved through the CIF are highlighted in yellow, while direct point-to-point connections are a highlight in green. Basically, with respect to M27, the final Design-Time support of the CERBERO framework is the one depicted in Figure 4.3, where you should notice that MDC has not been connected to SAGE. We opted for building the connection of MDC to CIF with the idea of providing MDC the possibility to connect to higher abstraction level tools and to assess, conversely from the CIF point of view, the possibility of using CIF also to make interoperable lower computation level framework components.

Figure 4.2: CERBERO toolchain for Design-Time Support (as foreseen at M18)

WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

Figure 4.3: CERBERO toolchain for Design-Time Support (as foreseen at M27)

Figure 4.4 illustrates the CERBERO tools that offer support at Run-Time as foreseen at M27:

- At System (of Systems) Level, MECA improves the resilience of human-machine teams by providing system, environmental and human monitoring and diagnosis, and high-level decision support in cases of unforeseen conditions and events, while DynAA explores different solutions at run-time to provide direct interaction with signals that come from the system and the environment.

- At the Computation Level several tools, for run-time support are present.

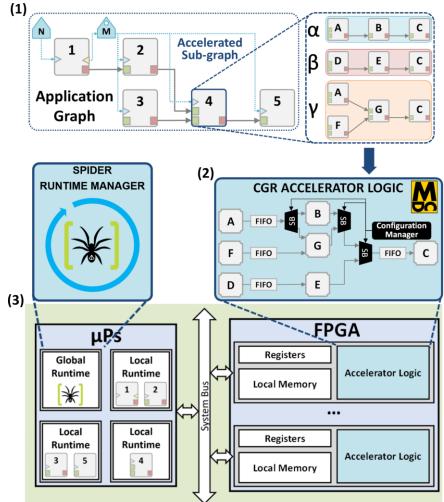

- SPIDER performs dynamic mapping and scheduling of dataflow applications on a parallel heterogeneous architecture.

- PAPIFY is meant to provide a large set of run-time execution information to SPIDER.

- MDC and ARTICo<sup>3</sup> deploy and configure proper engines over the physical substrate at design-time. These engines are used at run-time to execute all the actions needed to support run-time reconfiguration of the HW.

- JIT HW composition addresses fine-grain reconfiguration, providing a way to map circuits at run-time by composing small HW components laid on an overlay architecture. IMPRESS, a tool to implement JIT composable HW, allows reconfigurable module composition to generate custom overlays on the fly, without the need of predefined floor planning and inter-module communication description.

It is important to highlight that the final Run-Time support of the CERBERO framework has not changed from M18 to M27. Furthermore, the connection between SPiDER and ARTICo<sup>3</sup> is not available at the moment due to low-level incompatibilities between tools.

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

However, the ARTICo<sup>3</sup> runtime library provides similar rescheduling capabilities for FPGA-based processing, and it is being used currently while SPiDER is modified to support heterogeneous HW/SW processing properly.

Figure 4.4: CERBERO toolchain for Run-Time Support (as foreseen at M18 and M27)

Integration is based on methods and interfaces in agile cycles performing cross-layer integration and combining modelling, simulation, verification and code generation activities. It turned out to be essential before attempting the modelling, and hence integration efforts, to plan the following system characteristics:

- Functional and non-functional requirements.

- Available system libraries, including models that require new developments.

- System structure and composition.

- A unified naming convention for all properties and attributes.

- Open world assumption (more tools, more viewpoints).

Consequentially, constraints and KPIs (such as jitter, delay, latency, KPI, QoS, energy consumption) are verified before starting integration activities. All those activities have involved partners, and in particular technology/tools provider, participating to WP2-5.

Integration also involves gap analysis in order to discover gaps and overlaps and reveal points of interoperability. Understanding the opportunities for integration or gap-filling informs holistic trade-off decisions about integrating systems and capabilities [9].

Execution of CERBERO integration methodology adopts a Continuous Engineering approach that guarantees reuse of design time models for generating novel and more accurate design and operational models up to the runtime environment. In this deliverable, we provide an update on the integration methodology adopted.

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

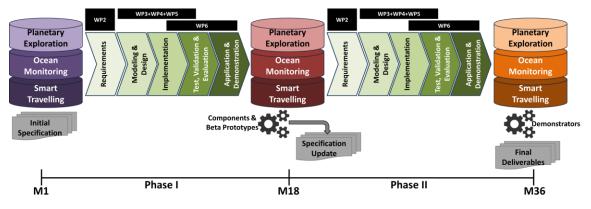

Semantic model-based integration supports cross-layer and cross-levels of abstraction modelling, usually dealing with system integration and system modelling. In this case, we leverage on ontologies "passing" relevant properties among layers and levels of abstraction. On the other hand, each layer (that can handle more than one model) has its own tools that usually much more compatible among each other and that should pass information by means of the same ontologies focusing on fast execution (important, e.g., for simulation). We implement a simplified version of ontology based on things with properties: each tool will look for relevant properties of intermediate models, constraints or KPIs from other tools (potentially in other layers/levels of abstraction); while the framework supports mapping model properties to tools/analysis namespace properties and provides shared directories for model exchange. The methodology has been co-refined together with project advance in cross-layer integration framework combining modelling, DSE, simulation, verification and code generation capabilities of CERBERO tools. Two iterations were planned during the total duration of the project, see Figure 4.5, delivering a "beta" and a "final" version of CERBERO integration strategies and internal interfaces. This report refers to integration activities up to M27. We are still closing the implementation step of the second phase of the project.

Figure 4.5: Iterative Development Scheme of CERBERO Integration Framework

# 4.3. Simplified Ontology-based Integration with Intermediate Representation

As mentioned earlier, integration is traditionally a complex engineering problem. It is characterized by several different accidental issues, as the usage of different modelling paradigm or languages, and thus require extreme effort to create and maintain necessary integration infrastructure. This is particularly true in the CPS environment where you need to combine components suitable for the different aspects of the CPS. These motivations led the designer to look for semantic integration of tools, and ontology-based integration is particularly suitable, in our opinion, to the case.

The term "ontology" derives from ancient Greek "onto", which means "being" and logos, which means, "discourse". Ontology -- or roughly the "science of stuff" and how it is represented -- used to be a rather obscure branch of philosophy. It still is in some cases, but

it is also an important and growing area of computer science and the web of things (WoT). Then, ontology has assumed other relevant meanings, such as:

"A formal shared and explicit representation of a domain concept."

or:

"A method for formally representing knowledge as a set of concepts within a domain, using a shared vocabulary to denote the types, properties and interrelationships of those concepts."

or:

"A formal way to describe taxonomies and classification networks, essentially defining the structure of knowledge for various domains."

Ontology-based data integration involves the use of ontology(s) to effectively combine data or information from multiple heterogeneous sources. So, we have started CERBERO integration efforts by creating a kind of ontology, by which we mean a collection of terms that identify the real things and relationships that are relevant to CERBERO-supported domains and industry-driven requirements. Maintaining an ontology design facilitates keeping track of the terms and ensures integration efforts quickly get up to speed.

CERBERO features heterogeneous technologies and tools. As discussed above, we retained the idea that model-2-model transformation would not necessarily be the main mean of communication between tools (also, the feasibility of having fully automated model to model transformations from the system of system level down to the hardware is unlikely). Instead, each tool will manage its own model(s), and the intermediate representation will be used to exchange "cross-layers" and "cross-models" information between tools.

The intermediate format is, therefore, necessary to achieve the mediation between the application's class model conceptualization and the common domain ontology conceptualization since objects in the original format cannot be handled directly in the framework [9]. Thus, CEBERO Interoperability Framework (CIF) follows the Resource Description Framework (RDF)-like meta-model underlying common ontology.

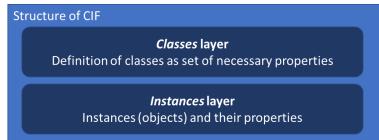

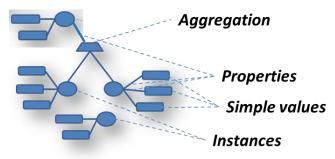

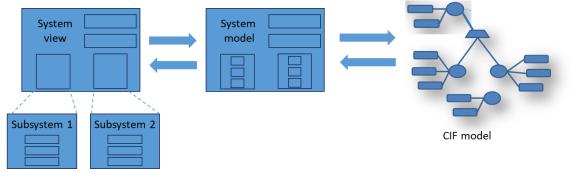

CERBERO integrated framework aims at one model for the entire platform. That is, a single model that maintains combined information provided from different connected tools. The key feature of CERBERO integrated framework is an ability to enrich this model by information provided by connected tools in tool-specific formats and to produce views of this model that are readable by connected tools. This functionality provided internally by the two-layered model structure [20] that separates instances, properties and aggregations (lower level) from classes (upper level) (see Figure 4.6).

Figure 4.6: Layers of the CERBERO Intermediate Format

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

Each instance in this model represents a thing that possesses one or more properties within corresponding namespaces. The property itself possess a value that can be either simple (integer, float, string, etc.) or object (another instance). Aggregations are special instances that serve to represent one-to-many relations between instances, so each aggregation can "contain" several instances. An example of instance-level CIF model is presented on Figure 4.7.

Figure 4.7: Example of CIF model

Classes are implemented using classification-by-property paradigm [20]. That is, any instance that possesses some predefined set of properties becomes an instance of the corresponding class. This predefined set of properties denoted as a class definition. The set of class definitions related to the specific namespace form ontology.

The system-level of abstraction can have a complete view of the system infrastructure. However, system level is not fully or directly aware of the "internals" of the underlying more detailed levels. Since the information available at the system level are relevant at lower levels, instances and properties in a model structure are inter-linked in such a way that allows navigation from one property in the system to another across different layers (see Figure 4.8).

Figure 4.8: From system view to CIF model

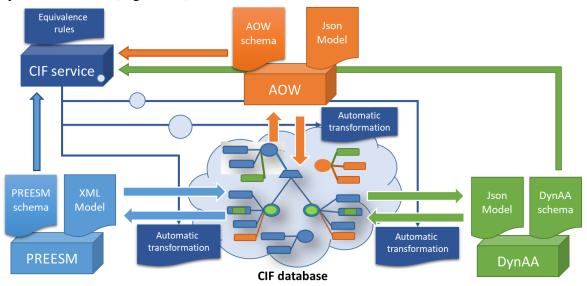

Ontology helps with revealing meaning and relations of each property from the whole graph by referring to a property by its name. All properties relevant to the model are present in the ontology. Ontologies can be either simplified (i.e. system model features only a subset of all properties of the real system), or full ontology where all properties in the system model are presented in the ontology. To enable interoperability between different tools and preserve the integrity of holistic model mappings between ontologies are provided. These mappings expressed through equivalence rules between classes and define relations between instances, classes and properties coming from different namespaces. As

a result, CIF database contain a single model combined from different viewpoints provided by different tools (Figure 4.9).

Figure 4.9: Example of ontology mapping between PREESM, AOW and DynAA

CERBERO proposes an application layer solution for interoperability. The key idea is to utilize semantics provided by existing specifications and dynamically wrap them in a middleware fashion into semantic services in such a way that automates interoperability without any modifications to existing standards, devices, or technologies, while providing to the framework user an intuitive semantic interface with services that can be obtained by executing all CERBERO technologies. In particular, a semantic layer is proposed for simple mapping of KPIs to model properties (i.e., connecting corresponding namespaces) as a semantic service; we may conventionally call that middleware the "CIF Service" The architecture of CIF service represented on Figure 4.10.

Figure 4.10: Architecture of CIF service

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

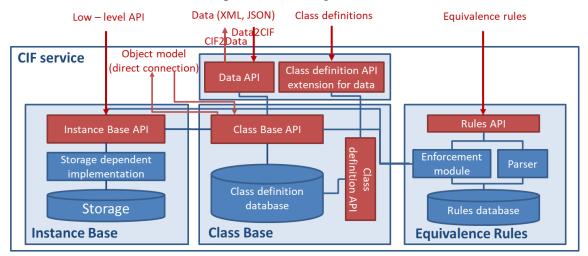

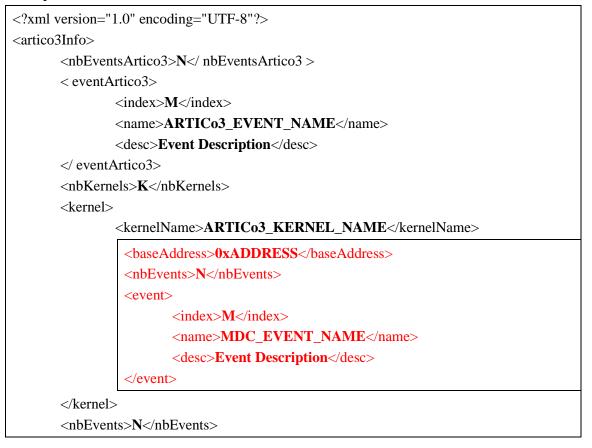

Tools can be connected to CIF directly by exposing their object models, or indirectly by translating their object models into suitable representation such as XML or JSON. In the second case one need additional layer translating data representation of object model into class base representation. This layer requires extensions of class definition semantic that is necessary for data-to-model translation. CIF service provide following APIs:

- Low-level API is designed to deal with low-level CIF model, i.e. add/remove/ change instances, properties and aggregations directly. This API is not supposed to use directly by external tools but can be useful for service extensions.

- Class definition API is designed to allow ontology definition through definition of related classes and classification by property paradigm.

- Class base API is designed for direct tool connection and allow import and export of part of tool model that is described using corresponding class definitions.

- Data API serves to import/export tool models from XML or JSON data files and requires from corresponding class definition extensions related to data-to-model translations.

- Equivalence rules API serve to maintain mappings between different ontologies (namespaces).

To sum it up, intermediate representation is the data or object model that one level of abstraction, layer or tool is going to produce and the other is going to consume. It may not necessarily be human understandable/comprehensible, but it's necessarily interpretable from one level/layer to another. In addition, feedback can be communicated to the originating level/layer to facilitates self-adaptivity and reconfigurability. To connect different layers or tools to the CIF service one should provide ontology of the respective layer or tool. This ontology expressed in a form of class definitions that utilizing classification-by-property paradigm. When class definition provided respective models can be exported/imported into intermediate format automatically. Ones several tools or layers describe their ontologies, it is possible to provide mappings between these ontologies in a form of equivalence rules between corresponding classes. When corresponding equivalence rules are provided, CIF service will care on automatic model transformation between connected tools.

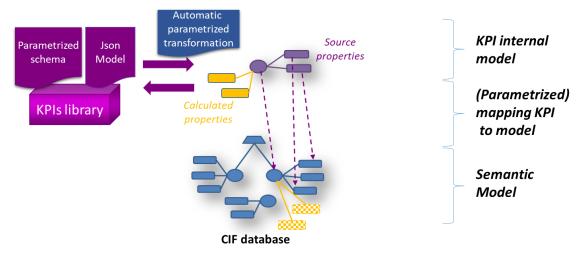

## 4.4. Mapping KPIs to Model

The evaluation of any Key Performance Indicator (KPI) out of its system model implies that designers must determine a way to calculate them. Such calculation can be expressed by means of a certain mathematical structure, or as we call it, an *algebra*. *Algebras* provided as mathematical expressions between properties of different instances having specific relations. Thus, algebra defines its own model including instances, classes and properties. In a case when there is no plain mathematical structure and calculation of corresponding KPI or its part should be held by some algorithm this algorithm can be described as a function possessing input and output parameters that can be described w.r.t to the same model structure. Models of the KPIs can be naturally expressed as a set of parametrized class definitions. Ones all parameters are given one can instantiate these definitions adding them to the class definition database through corresponding API. Furthermore, these definitions can be mapped to the model by equivalence rule mechanism.

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

Thus, to map KPI to the model one should instantiate class definitions provided by KPI ontology and map these definitions to the model (see Figure 4.11). Ones mapping provided, application serving for corresponding KPI calculation can read the model, perform calculation and return the results back to the CIF.

Figure 4.11: Mapping of KPI to the model

## 4.5. OS Qualified as a Toolchain Host

CERBERO array of tools and technologies widely support both Windows and Linux. However, Windows has been qualified by the consortium as the host operating system of choice for the project since it has a larger market share and is more familiar with respect to Linux, more feature-complete, enjoys commercial support, and is not subject to the disintegrity imposed by a wide range of different Linux distributions that are only maintained by their respective communities.

## 5. Internal Interfaces

Cyber Physical Systems (CPSs) are an evolution of embedded systems and are based on a tight combination of collaborating computational elements (i.e. micro computing units or embedded systems interconnected by a communication system) that control physical entities. Therefore, in CPS all types of smart equipment (i.e. sensors, actuators, devices, machines, robots) are interconnected creating a smart community with data capture and action capability from/to the physical world.

A CPS-based architecture for manufacturing is made of smart but independent manufacturing components without any knowledge of the role they have to play together in the real application. Ontologies can supply such kind of knowledge, playing a very crucial role in CPS design.

Ontology in computer terms is concerned with the meaning of and the relationship between entities. It derives its importance from its ability to organize raw or unstructured data by semantics (i.e. meaning, such as classes, properties or attributes, and relationships), rather than merely by strings or keywords, thus facilitating more efficient data operations (storing, querying, sending and receiving). An ontology is often referred to as a "schema".

Ontologies are typically far more flexible than class representations and hierarchies as they are meant to represent information coming from all sorts of heterogeneous data sources. Class hierarchies, on the other hand, are meant to be fairly static and rely on far less diverse and more structured sources of data.

Therefore, CERBERO consortium postulates simplified ontologies as the right tool to implement cross-layer information sharing and data flow in order to implement internal interfaces and hence realize the CERBERO holistic integration methodology. As discussed above, by simplified ontology we mean using things with properties where all analysis viewpoints are defined by a set of properties and all objects that hold them.

## 5.1. Low-Level Instance Base Interface

As mentioned in Section 4.3 low-level interface intended for direct manipulation with basic CIF structures that includes instances, properties and aggregations.

**Instance** – represents a simple object that has unique identifier (UID) that allow to distinguish one instance from another. Instances can possess properties.

**Property** - represents a relation between instance (property owner) and property value, that can be either simple value, another instance or aggregation. Each property has name and namespace. Any instance can possess (be owner of) only one property with specific name within specific namespace.

**Aggregation** – generalization of the instance that served to represent one-to-many relations. May contain any number of members that can be either instances or simple values. In the current implementation cannot possess properties. The question on whether aggregation can or cannot possess properties is under investigation.

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

The low-level interface includes methods to get/create/delete instances, properties, aggregations and namespaces. It also includes additional methods that are created to fulfill functionality required by high-level APIs such as class base or equivalence rules. This interface in general is not supposed to be used by CIF connected tools directly, unless CIF connected tool do not introduce extension to CIF itself.

## 5.2. Ontology and Class Definition Interface

Many software packages are now available for creating ontologies, among which are:

- Stanford University's Protégé (<u>https://protege.stanford.edu/</u>), a free, open-source ontology editor.

- TopBraid Composer from TopQuadrant. (<u>https://www.topquadrant.com/products/topbraid-composer/</u>).

- Generally, any text editor.

Apart from RDF/XML, RDF ontologies can also be expressed in human-readable formats, for example JSON that is also popular format for data exchange.

Before delving into a full example of a JSON-represented ontology, here below is a quick recall of the most relevant terminology:

- **JSON:** is a lightweight format for data exchange (as XML, but less verbose yet more human-readable). [By "data" we mean is the set of classes and attributes that will be shared by tools and technologies that interoperate within the CERBERO framework.].

- **JSON-Schema:** a JSON document according to which the ontology is defined. [For example, if there are required or mandatory attributes if they are of number datatype, if they can be null, etc.] In XML equivalence, that would correspond to an XML schema or a Document Type Definition (DTD).

- **Ontology:** formally defines a common set of terms used to describe and represent a domain (according to the JSON-Schema).

- **Instance of Ontology:** a specific element of an ontology.

Here we provide a simple Ontology such as representing an instance of DynAA task class that is defined as all instances having "name", "type" and "params" properties within DynAA namespace. Here name and type are simple properties having values of string type and params is object property which value is an instance of DynAA param class that have integer property load and optionally integer property factor. An instance of this class looks like:

```

{

"name": "Split0",

"type": "Split",

"params": {

"factor": 8,

"load": 2

}

```

}

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

Following is a JSON Schema that describes the Ontology:

```

{

"namespace": "dynaa",

"class": "task description",

"schema": {

"properties": [

{

"name": "name",

"optional": false,

"value": {

"type": "str",

"optional": false,

"collection": null,

"constrains": [],

"default": null,

"object": null

}

},

{

"name": "type",

"optional": false,

"value": {

"type": "str",

"optional": false,

"collection": null,

"constrains": [],

"default": null,

"object": null

}

},

{

"name": "params",

"optional": true,

"value": {

"optional": false,

"type": "object",

"collection": null,

"constrains": [],

"default": null,

"object": {

"namespace": "dynaa",

"class": "param description"

}

}

}

]

}

}

{

"namespace": "dynaa",

"class": "param description",

```

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

```

"schema": {

"properties": [

{

"name": "factor",

"optional": true,

"value": {

"type": "int",

"optional": false,

"collection": null,

"constrains": [],

"default": 1,

"object": null

}

},

{

"name": "load",

"optional": true,

"value": {

"type": "int",

"optional": false,

"collection": null,

"constrains": [],

"default": 0,

"object": null

}

}

]

}

}

```

By using the schema, a computer program can validate, understand, and process the data file to purposes of creating a computational model, transferring data, analysis, simulation, and reporting. The use of schemas makes the modelling tool more generic, and independent of a specific file format. This is very important to increase the interoperability between tools, modelling layers (HW/SW), and modelling views.

CERBERO intermediate format introduce following format of class definitions (schemas): CIF class definition file includes following fields:

- "namespace" namespace for which belongs class definition.

- "class" name of the class.

- "schema" schema of the class.

Schema consists of properties definitions enlisted under "properties" key, where each property includes following fields:

- "name" name of the property.

- "namespace" optional. Should be provided if property has different namespace (not same as defined in the schema namespace).

- "optional" true/false indicates if property is optional or not. Instance of respective class may not possess optional properties.

- "value" describes value of the instance.

Value field includes following properties:

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

- "type" describes type of property value may be either "str", "int", "float" or "object", indicating that related property should have value of corresponding type.

- "optional"- true/false indicates that value is optional (i.e. can have "null") value or not.

- "collection" "set"/ "list"/null indicates that property points to collection of objects of corresponding type. Null value in this field indicates that property possess single value. Properties possessing collection values (having collection "set" or "list") possessing aggregation value in the instance base.

- "constrains" set of constraints on property value (functionality of this field does not implement yet).

- "default" default value of the property. Optional. If provided and property has null value, then default value used instead of null.

- "object" either null (for simple types) or object specification (for object type).

Object specification consist of two fields:

- "namespace" namespace for which belongs object value.

- "class" name of the class for which belong object value.

## **5.3.** Class Base Interface for Directly-Connected Tools.

Class base interface introduce methods to deal with objects of specific classes. Each class should be described by providing corresponding class definition. As mentioned in section 4.3 classes are implemented using classification-by-property paradigm, i.e. each instance in the instance base that possess specific set of properties described in some class definition is the object of the corresponding class. In order to use class base interface direct-connected tools should expose their objects as Python dictionaries. Class base interface includes following methods:

- "create\_object(self, namespace, class\_name, dct)" creates object of specific class within specific namespace from Python dictionary object. Fails if Python dictionary object does not include specific set of properties described in class definition.

- "get\_object(self, namespace, class\_name, cif\_instance)"

obtains object of specific class within specific namespace from specific CIF instance. Fails if provided instance does not possess necessary set of properties described in class definition.

- "get\_objects(self, namespace, class\_name)" obtain all objects that meets specific class definition within specific namespace.

- "remove\_objects(self, uids)" removes instances of corresponding objects including corresponding properties.

- "update\_object(self, uid, dct)" update object by setting property values according to values provided by Python dictionary object.

## **5.4.** Data Serialization and Data Interfaces

Successful tool integration necessitates that system model data to be serialized or rendered into a preferably standard, format or syntax that can be parsed later and transformed into another format as per need of subsequent layers.

JSON representation of a set of *RDF* triples as a series of nested data structures has become increasingly popular as a data serialization format thanks to its more lightweight structure compared to XML, making it a useful format for data exchange in a way that requires less bandwidth than a bulky XML document. Thus, CERBERO choose JSON format as a primary format for data serialization. To enlarge compatibility with CERBERO tools that using XML as primary serialization format automatic XML-to-JSON and JSON-to-XML translators are provided.

However, JSON data format (especially after XML-to-JSON translation) are lacking several important features that are natural parts of underlining object models. For example, JSON format lacking possibility of referencing object that are defined in other parts of JSON document. To overcome difficulties introduced by the missing features we provide class definition extension for data. This extension provides following properties:

On the schema level:

- "name" name of the schema. Since objects of the same class can be serialized with different data formats several different schemas can be provided to deserialize these objects. These schemas distinguishing by their names.

- "representation" defines properties representation into JSON serialized object. Includes following sub-properties:

- "type" can be one of "key\_value\_base" / "property\_base" / "mixed".

Describing data representation type: "key\_value\_base" is a native JSON representation, where JSON key describes property name and JSON value describes property value; "property\_base" is a special representation often produced by XML-to-JSON converters, where each property defined by two JSON key-value pairs one having property name as its value and another having property value as its value; "mixed" is a representation where both types of representation are used.

- "base\_key" parameter that defines JSON key which value defines class of JSON serialized objects. This value will be parsed according to corresponding schema all other JSON key-value pairs will be ignored.

- "key\_prefix" parameter that defines prefix that should be stripped from JSON key on JSON-to-CIF conversion or added to JSON key on CIFto-JSON conversion.

- "key\_value\_base" describes parameters specific for "key\_value\_base" representation of properties. Includes "base\_key" and "key\_prefix".

- "property\_base" describes parameters specific for "property\_base" representation of properties. Includes "base\_key", "key\_prefix" and two additional parameters:

- "property\_name\_key" describes which JSON key used by parser to identify key-value pair that defines property name as its value.

- "property\_value\_key" describes which JSON key used by parser to identify key-value pair that defines property value as its value.

- "keys" define list of unique keys that allow to distinguish one object of corresponding class from another. Includes following sub-properties:

- o "name" name of the key.

- "properties" defines list of properties which form unique identifier of the object of corresponding class.

On the property level:

- "representation" defines representation of the specific property if schema has "mixed" type of representation.

- "base\_key" same meaning as "base\_key" in representation description but applied only to specific property.

- "key\_prefix" same meaning as "key\_prefix" in representation description but applied only to specific property.

On the object level:

- "schema" defines name of the schema of the nested JSON object. Object will be parsed according to corresponding schema.

- "extensible" true/false. Defines if nested object can represent a new object of corresponding class (true), or only reference to existing object of corresponding class (false).

- "id type" defines how nested object are identified and can be either:

- "object" nested object itself provided according to corresponding schema,

- "uid" reference to the existing instance in the CIF database provided as UID of the CIF instance,

- "key"-indicates that only several properties are provided and set of provided properties includes at least properties enlisted in the unique key provided in the "id\_key" property value,

- "key\_property" indicates that provided value of a property that uniquely identify the object. In this case "id\_key" property refers to key that based on one property only.

- "id\_key" required if "id\_type" property has value "key" or "key\_property" defines a name of the unique key in the corresponding schema.

CIF data interface expose exactly same methods as class base interface, however these methods gets schema name as additional parameter and using JSON or XML instead of Python dictionary objects.

## 5.5. Ontology Alignment and Equivalence Rules

Ontology alignment, or ontology matching, is the process of determining correspondences between concepts in ontologies. In the tool-integration context involving many tools providing their own ontologies, ontology matching has taken a critical place for helping heterogeneous tools to interoperate. CIF provides ontology alignment as set of the equivalence rules between objects of two or more classes. Equivalence rules allow automatic transformation of objects between different tools, levels and layers of abstractions. Set of the rules, describing all equivalence relations between objects of all classes of two different namespaces, represents a mapping between corresponding ontologies. Albeit, different tools and languages for ontology alignment exists, CERBERO found that existing tools and languages are not suitable for CIF simplified ontologies for various semantic and syntactic reasons. Thus, instead of trials to adopt existing tools and languages to ontology alignment CERBERO decided to develop new equivalence rules language based on mathematical background and language developed by IBM for metrics library. This choice supported by common principles that lies under SEMI developed by IBM and CIF developing by CERBERO. Moreover, specification of this kind of language can be further reused to develop KPI library language.

CIF provide following syntax of equivalence rules.

```

• Main rule syntax:

ns1:class1 operator ns2:class2 [*...] [ON ...] [IMPLYING

...];

ns1, ns2

- names of namespaces

class1, class2 - names of classes

operator

- one of: ===, <==, ==>, <==>

[*...]

- optional multiplication part

- optional "on" part

[ON ...]

[IMPLYING ...]

- optional "implying" part

- termination symbol

Optional multiplication part syntax:

* ns3:class3 | int expression [*...]

- name of namespace

ns3

- name of class

class3

|int expression - any integer expression that can be provided instead of

ns3:class3

[*...]

- optional multiplication part

Optional on part syntax:

ON (bool expression [, bool expression])

bool expression - any bool expression

[, bool expression] - optional additional comma-separated bool

expressions

• Optional implication part syntax:

IMPLYING (implication [, implication])

```

• Implication syntax 1:

#### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

```

ns1:class1.property expr1 operator

ns2:class2.property expr2 [*...] [ON ...] [IMPLYING ...]

ns1, ns2 – names of namespaces

class1, class2 - names of classes

operator - one of: ===, <==, ==>, <==>

property expr1, property expr2 - expressions defining

(sub)properties names

- optional multiplication part

[*...]

- optional "on" part

[ON ...]

- optional "implying" part

[IMPLYING ...]

• Implication syntax 2:

ns1:class1.property expr1 = gen expression

- name of the namespace

ns1

- name of the class

class1

property expr1 - expression defining (sub)property name

gen expression - general mathematical expression

```

#### Equivalence rule semantics.

Semantics of main rule operators (void multiplication part).

- === means that corresponding classes are equivalent, i.e. each instance of class 1 is also instance of class 2 and vice versa.

- ==> means that class 2 equivalent to class 1, i.e. each instance of class 2 is also instance of class 1, but instance of class 1 is equivalent to instance of class 2 only if both met matching criteria provided in "on" part.

- means that class 1 equivalent to class 2, i.e. each instance of class 1 is also instance of class 2, but instance of class 2 is equivalent to instance of class 1 only if both met matching criteria provided in "on" part.

- <==> means that instance of class 1 is equivalent to instance of class 2 only if both met matching criteria provided in "on" part.

#### Semantics of multiplication part.

Multiplication part change equivalence rules operator semantics in the following sense:

- when multiplication part contains class reference this means that class 1 equivalent to cartesian product of instances of class 2 and class 3, each instance of class 1 has two different instances (one of class 2 and one of class 3) as his counterpart with respect to corresponding relation operator.

- when multiplication part contains integer expression this means that each instance of class 1 corresponds to number of instances of class 2, and this number defined by integer expression that may depend on properties of corresponding instances.

#### Semantics of "On" part.

"On" part can include several logical expressions that treated as matching criteria between instances that are equivalent according to corresponding rule. These expressions can be treated as one single expression with "and" operator between corresponding parts.

### WP5 – D5.1: CERBERO Holistic Methodology and Integration Interfaces (Final Version)

#### Semantics of implications.

Implication of kind 1 (syntax 1) can be treated as nested equivalence rule and define equivalence relations between property values of instances of corresponding classes. Implication of kind 2 (syntax 2) define property value that should be assigned during rule execution process. This value is a result of calculation of general mathematical expression.

## 6. Direct Tool Integration Holistic Methodology