#### Analysis of a Heterogeneous Multi-Core, Multi-HW-Accelerator-Based System Designed Using PREESM and SDSoC

Leonardo Suriano

Universidad Politécnica de Madrid

#### Introduction

#### Embedded World

...and many others

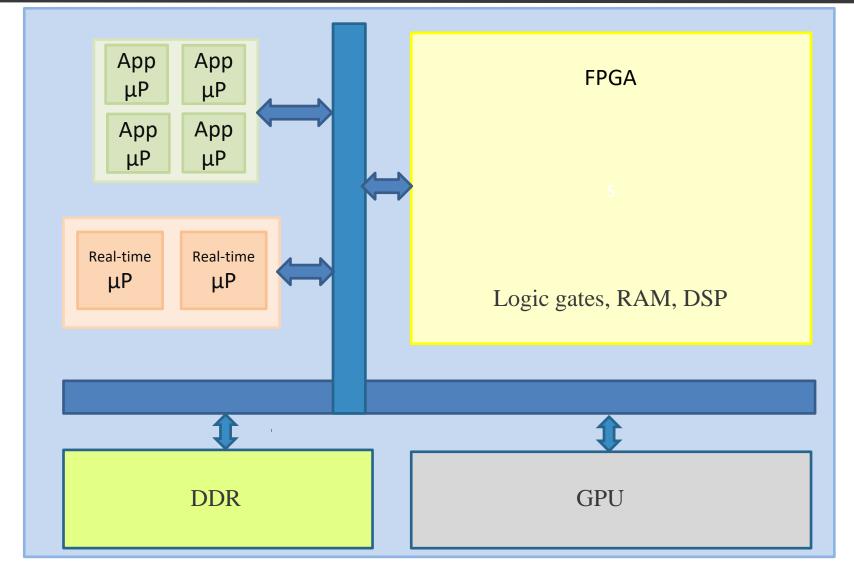

## **Heterogeneous devices**

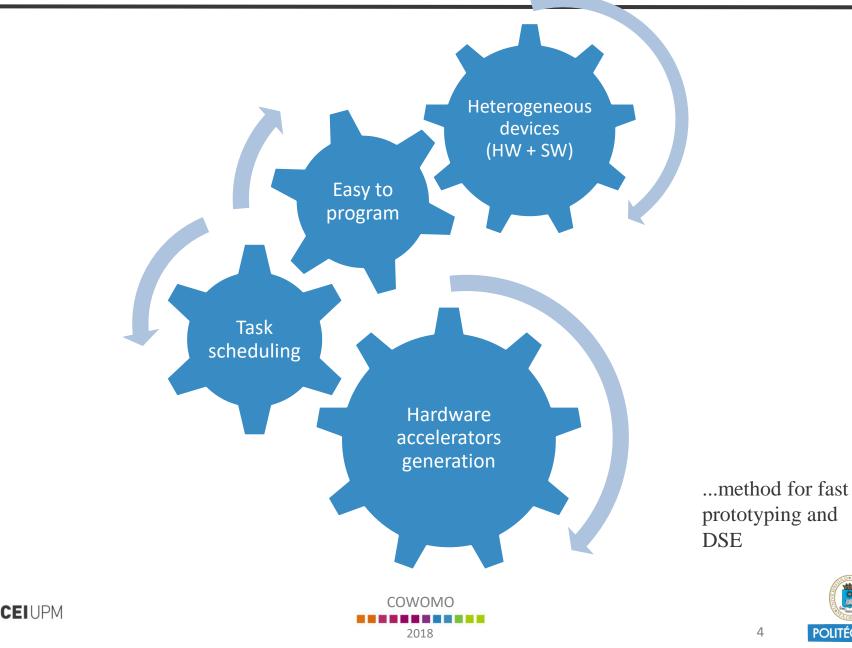

#### GOAL

# **Used Tools**

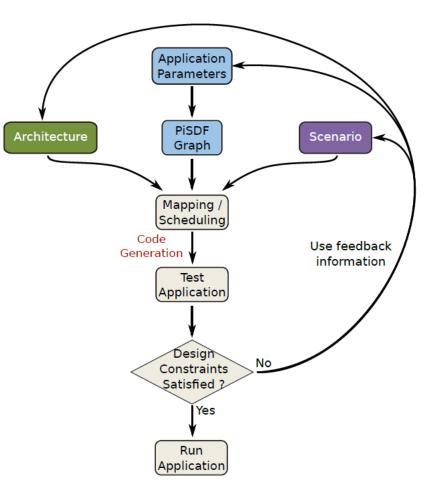

Rapid prototyping of software applications enabling:

- deadlock-free code generation using **PiSDF MoC**

- custom hardware acceleration and generation

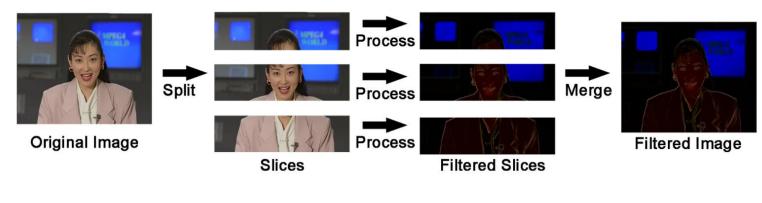

# **Video Processing Application**

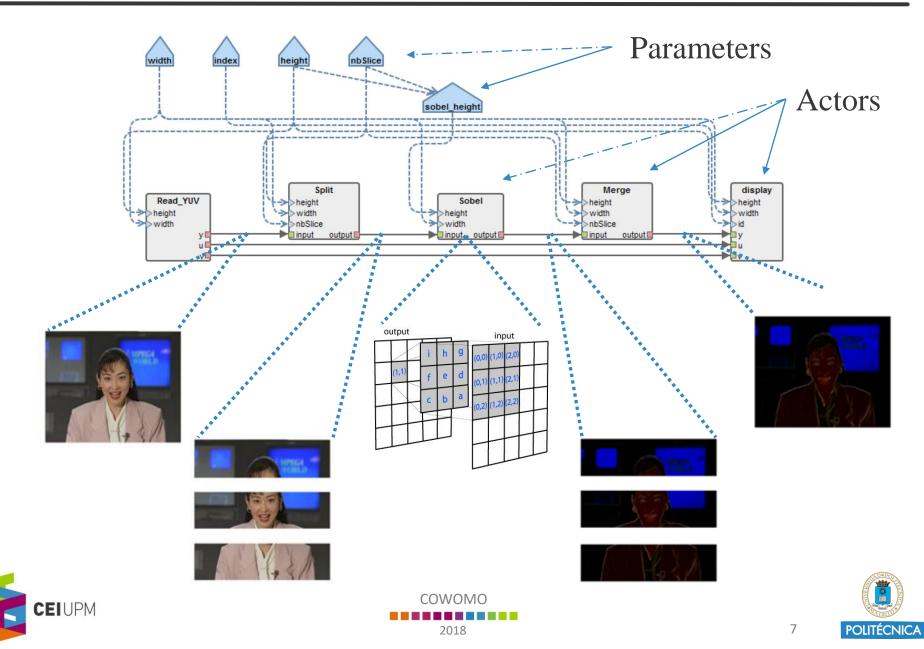

# **Actors Specification**

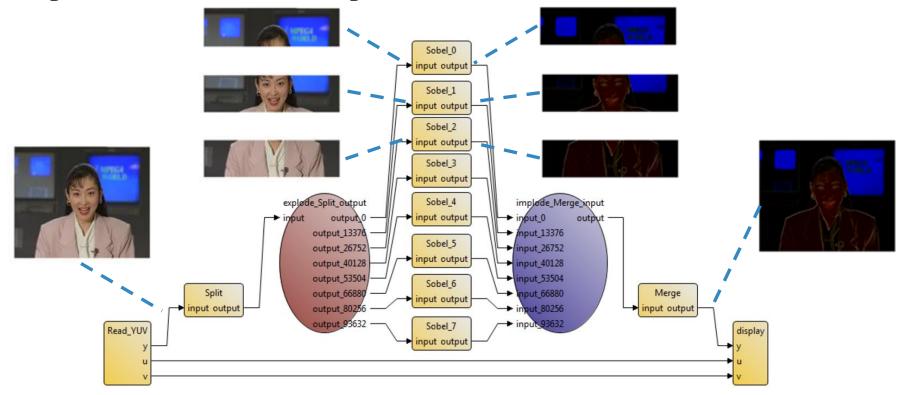

# **Exposed parallelism**

**Equivalent single-rate graph** where each edge has equal production and consumption rates of token.

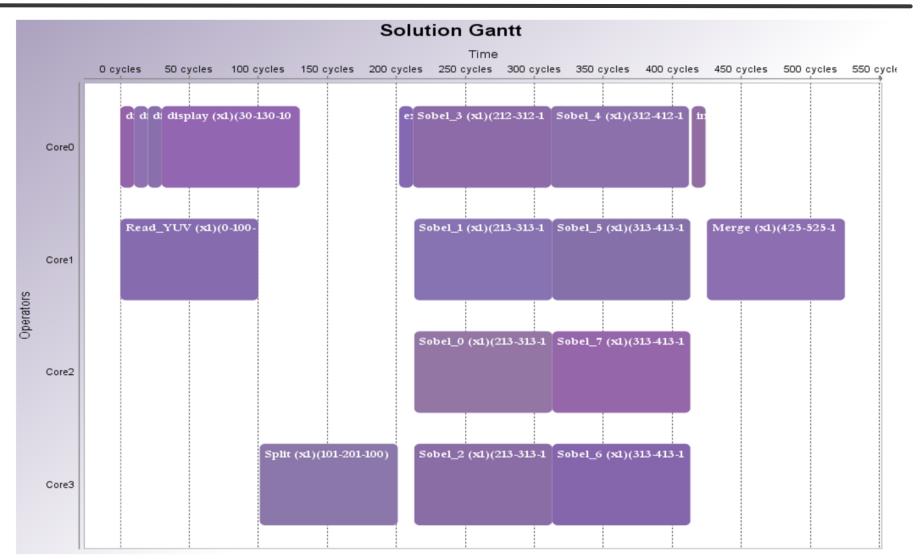

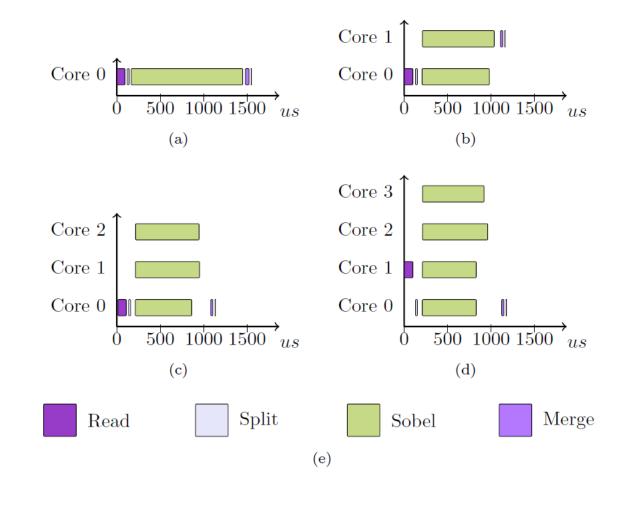

## **Actors scheduled**

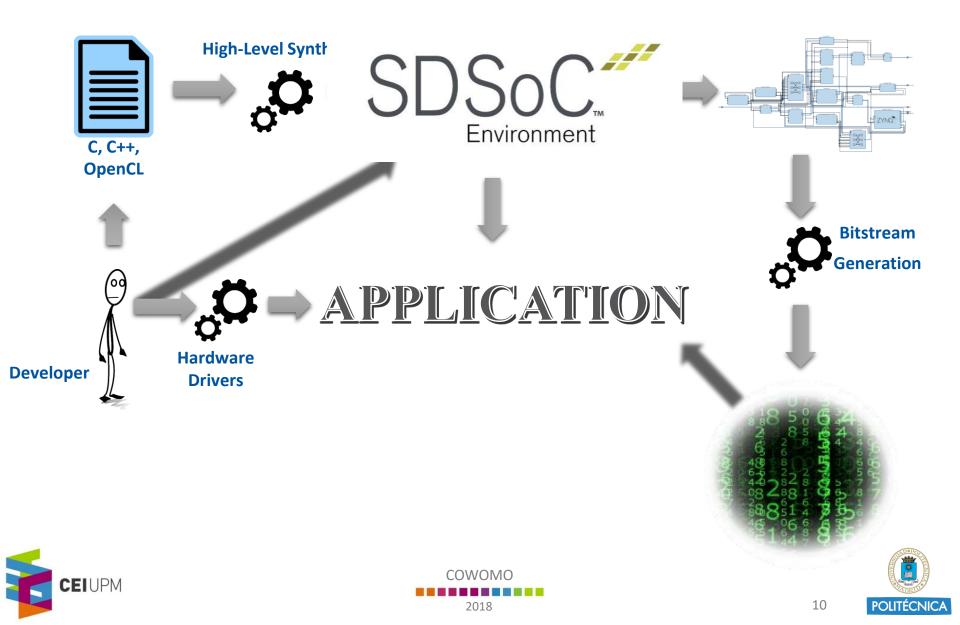

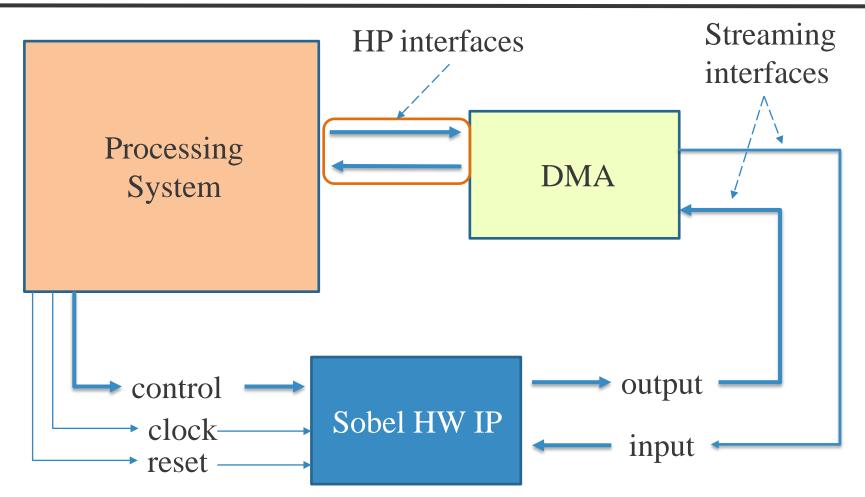

# **High Level Synthesis and SDSoC**

# From PREESM to SDSoC

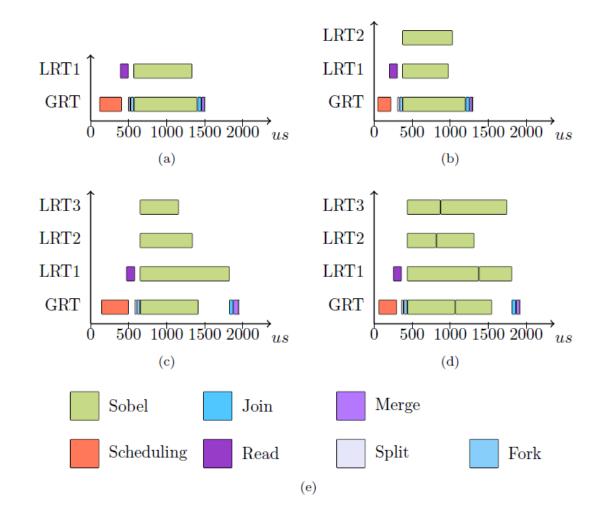

### **Design Space Exploration**

#### **Results on Ultrascale+ (static)**

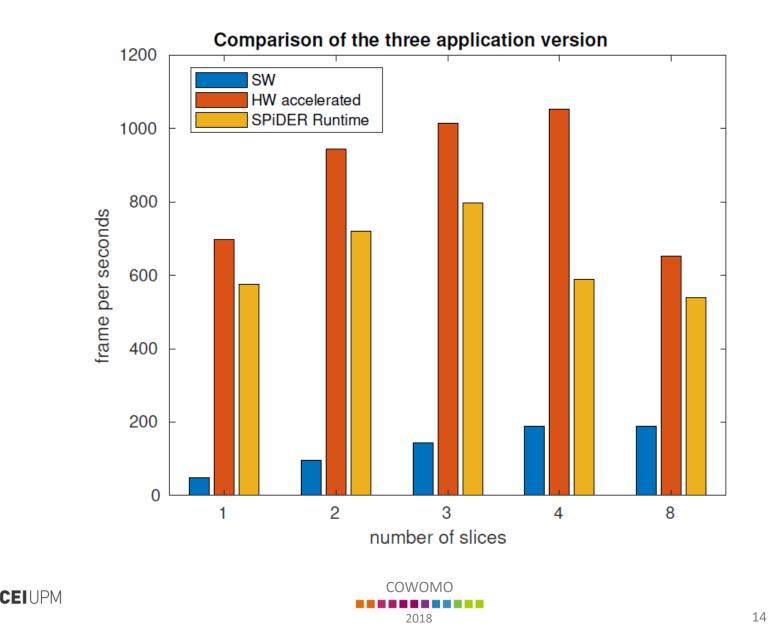

# Comparison

# **Results on Ultrascale+ (runtime)**

COWOMO

2018

# Thank you for your attention