HiPEAC 2020 20-22 January, 2020, Bologna, Italy

#### CERBERO H2020 Project – Tutorial: Design Flow for Heterogeneous Embedded Computing Infrastructures

Tiziana Fanni<sup>2</sup>, Daniel Madroñal<sup>1</sup>, Maxime Pelcat<sup>3</sup>, Alfonso Rodriguez<sup>1</sup>, Carlo Sau<sup>4</sup>, Claudio Rubattu <sup>23</sup>, Leonardo Suriano<sup>1</sup>

<sup>1</sup>Universidad Politécnica de Madrid, <sup>2</sup>Università degli Studi di Sassari, <sup>3</sup>IETR INSA-Rennes, <sup>4</sup>Università degli Studi di Cagliari

Horizon 2020 European Union funding for Research & Innovation

• Here is a Martian robot

- Here is a Martian robot

- it has wheels, a robotic arm, many sensors, and a complex control and computing system

**∲-**»)

- Here is a Martian robot

- it has wheels, a robotic arm, many sensors, and a complex control and computing system

- Here is what can happen to this robot

(•۸

- Here is a Martian robot

- it has wheels, a robotic arm, many sensors, and a complex control and computing system

- Here is what can happen to this robot

- one of its cameras can be occluded

**∳-**))

#### • Here is a Martian robot

- it has wheels, a robotic arm, many sensors, and a complex control and computing system

- Here is what can happen to this robot

- one of its cameras can be occluded

- one of its wheels can be blocked

**₩-)**)

#### • Here is a Martian robot

- it has wheels, a robotic arm, many sensors, and a complex control and computing system

- Here is what can happen to this robot

- one of its cameras can be occluded

- one of its wheels can be blocked

- one **arm** segment can be stuck

**\/-**))

#### • Here is a Martian robot

- it has wheels, a robotic arm, many sensors, and a complex control and computing system

- Here is what can happen to this robot

- one of its cameras can be occluded

- one of its wheels can be blocked

- one **arm** segment can be stuck

- one **motor** can overheat

**\/-**))

#### • Here is a Martian robot

- it has wheels, a robotic arm, many sensors, and a complex control and computing system

- Here is what can happen to this robot

- one of its cameras can be occluded

- one of its wheels can be blocked

- one arm segment can be stuck

- one **motor** can overheat

- on **processing** itself, a region of hardware can be temporarily or permanently unavailable

- in particular because of ionizing particles

- How do we resume the mission in case of problems?

- or at least use **remaining robot capacities** for future operations?

- How do we resume the mission in case of problems?

- or at least use **remaining robot capacities** for future operations?

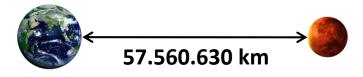

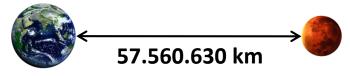

- By the way, radio-controlling is not feasible

- light return trip to earth is 9 minutes so ...

- How do we resume the mission in case of problems?

- or at least use **remaining robot capacities** for future operations?

- By the way, radio-controlling is not feasible

- light return trip to earth is 9 minutes so ...

- Proposition

- Self-adaptation support and CERBERO tooling

- HW/SW reconfiguration for reliability and performance

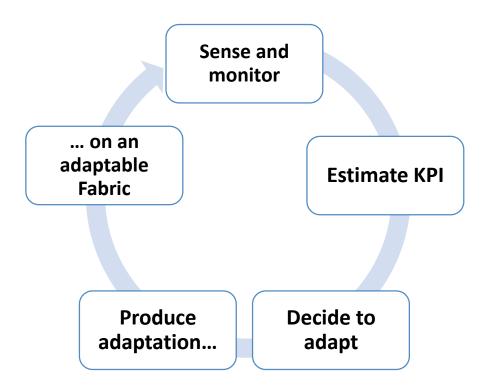

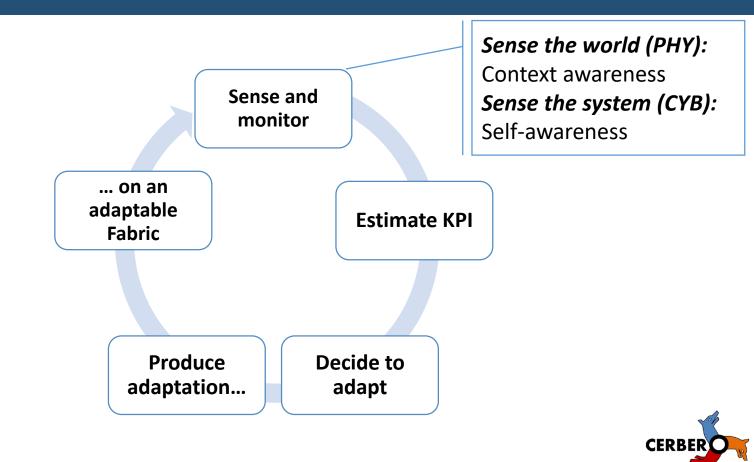

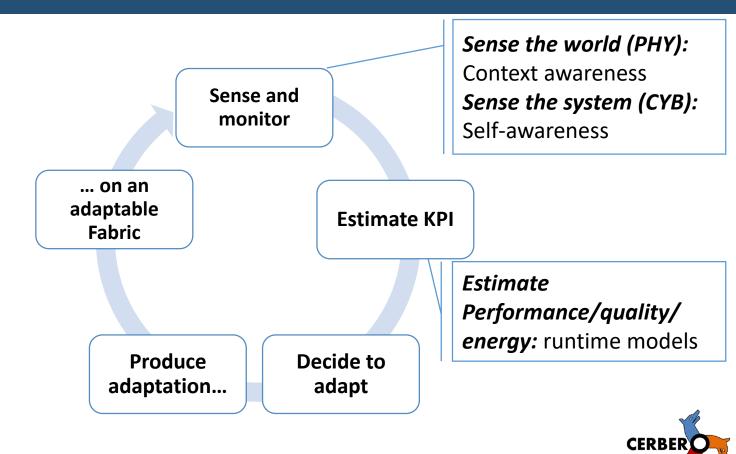

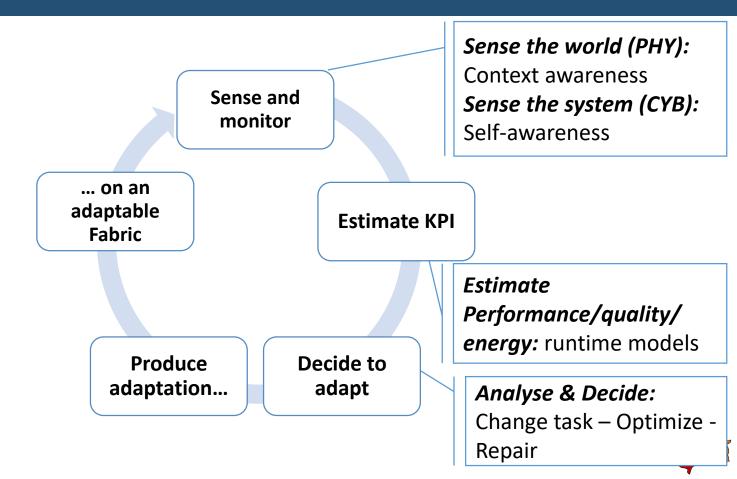

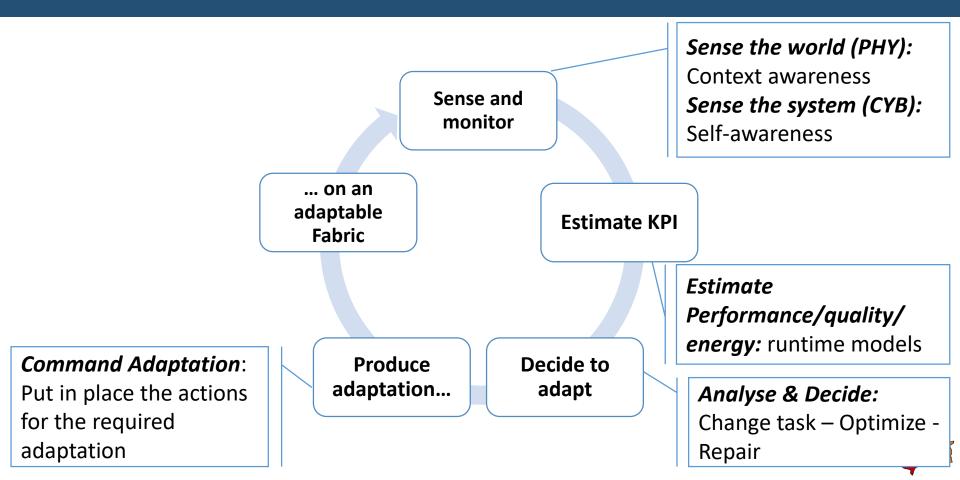

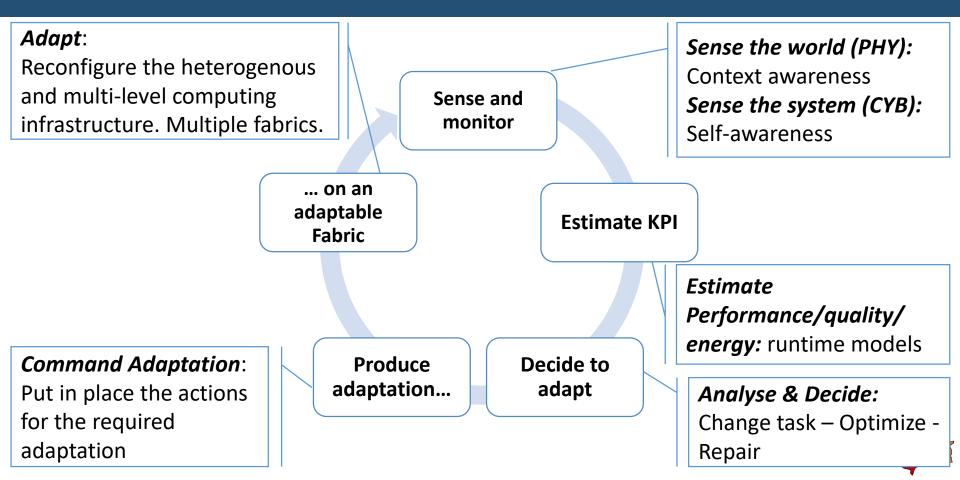

## **Ultimate Goal: Self-Adaptation Support**

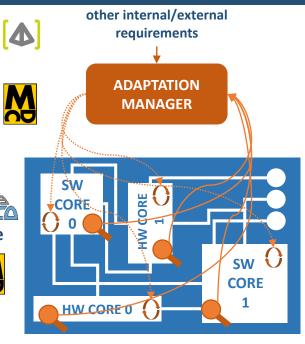

Self-adaptation: *runtime* action *changing structure, functionality and/or parameters of a system*, according to environment, user or self-sensing info.

[F.D. Macías-Escrivá, et al. "Self-adaptive systems: A survey of current approaches, research challenges and applications" In Expert Systems with Applications, 2013]

System self-adaptation: awareness + reconfiguration.

- Reconfiguration → decided *inside the CPS* by a smart *self-adaptation manager (hierarchy of managers)*.

- Decisions → based on run-time Key Performance Indicators (KPIs) measurements and estimations.

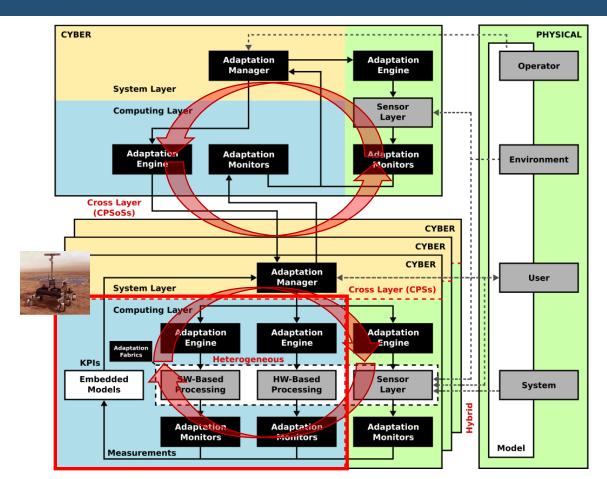

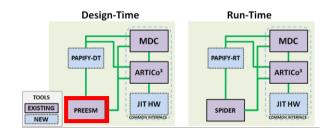

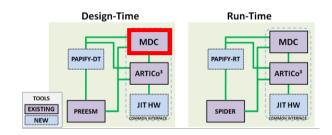

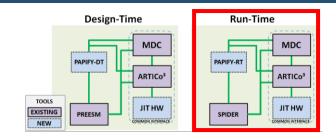

### **CERBERO Self-Adaptive Multi-Level Infrastructure**

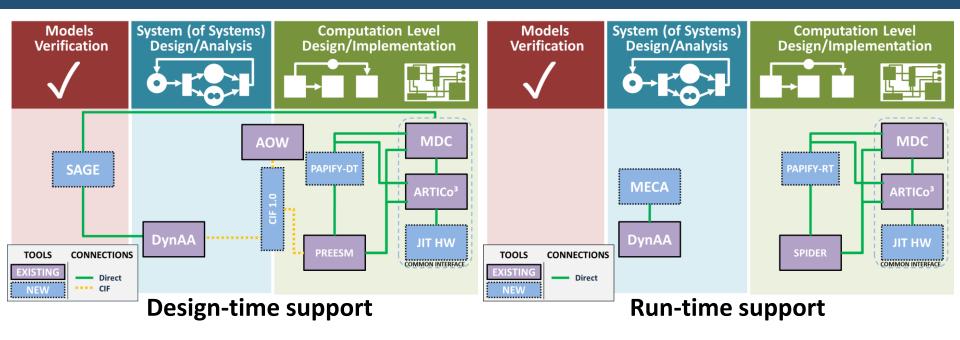

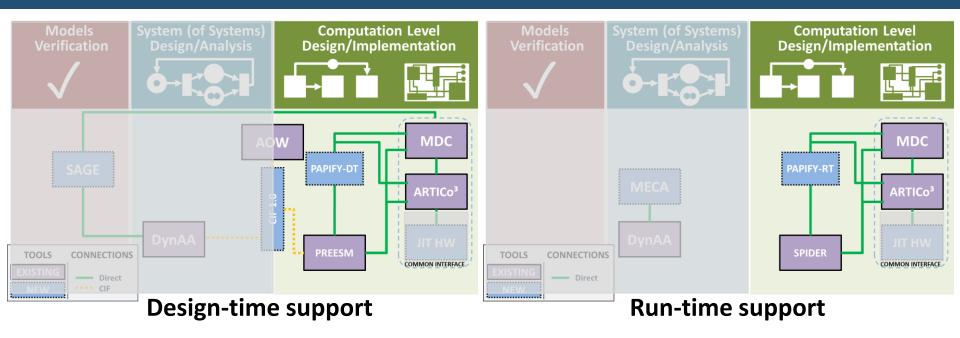

### **CERBERO Framework**

### **CERBERO Framework**

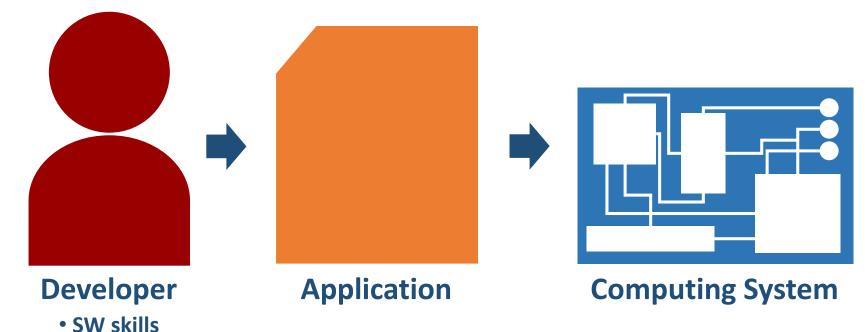

**Developer**

### Developer

• SW skills

#### **Application**

HW notions

CERBER

- SW skills

- HW notions

#### **Application**

#### Developer

- SW skills

- HW notions

#### **Application**

Adaptivity

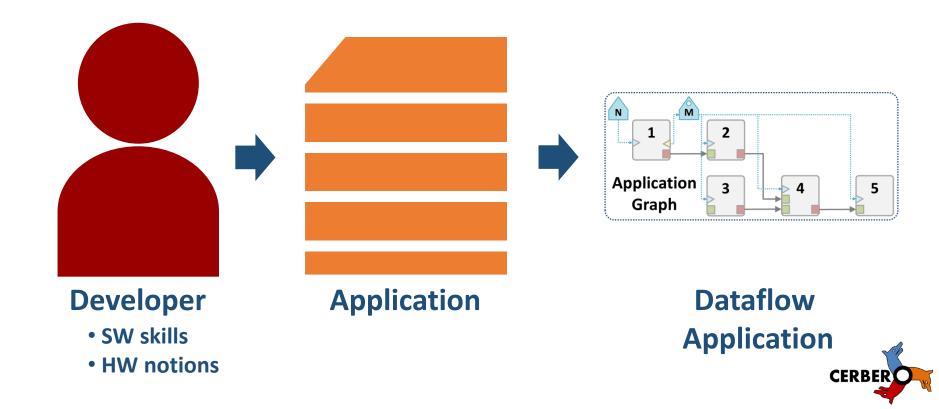

#### Developer

- SW skills

- HW notions

#### **Application**

#### Adaptivity

Heterogeneity

#### Developer

- SW skills

- HW notions

#### **Application**

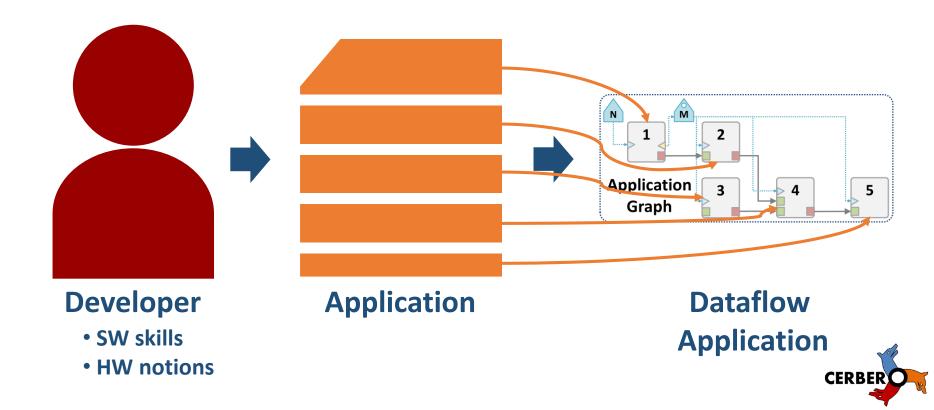

#### **Developer**

- SW skills

- HW notions

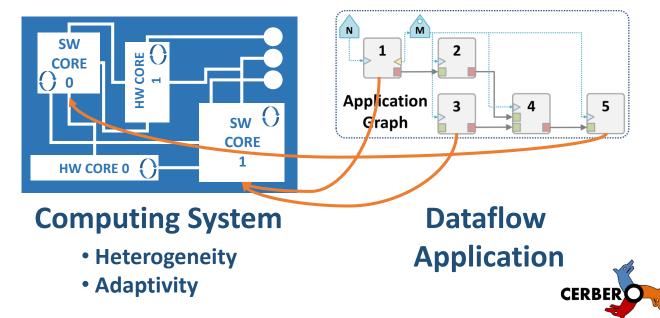

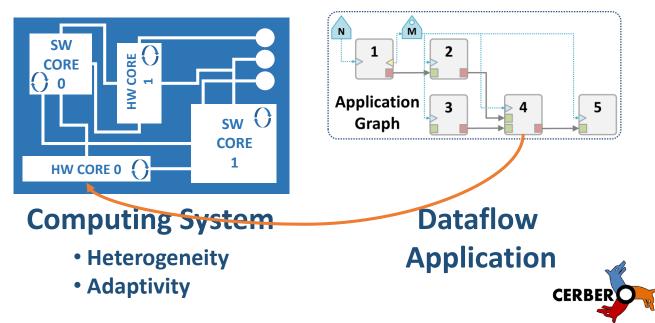

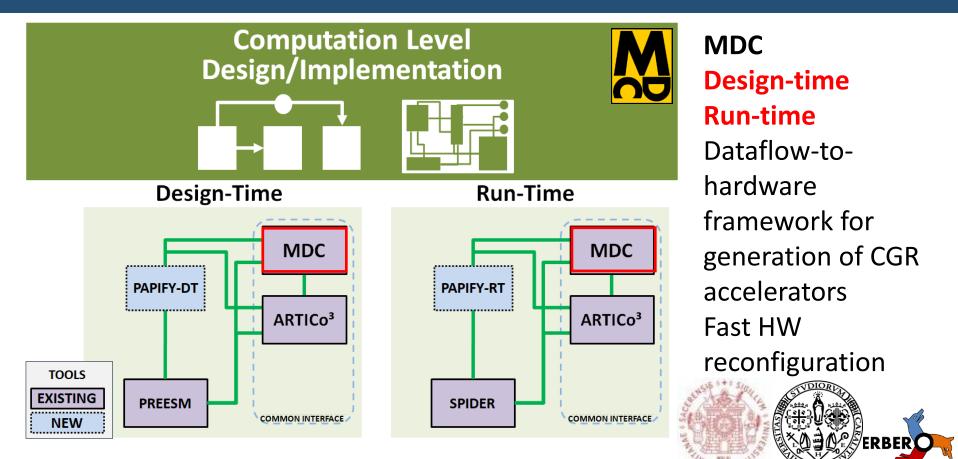

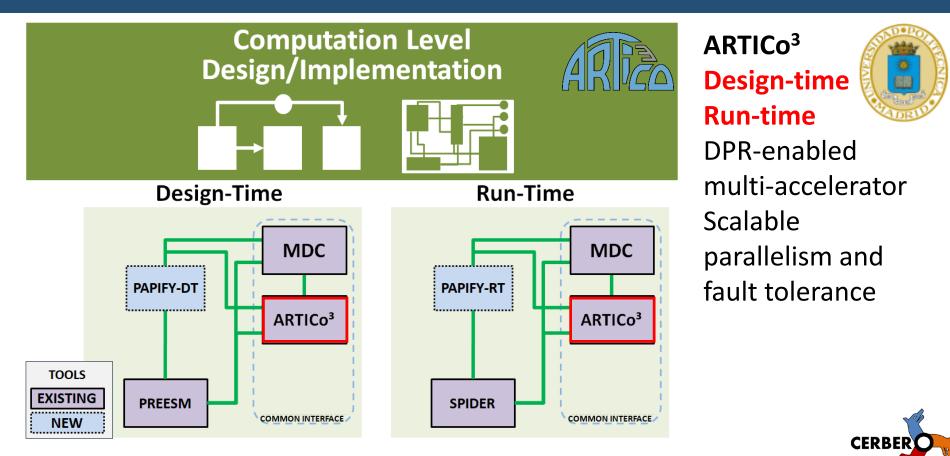

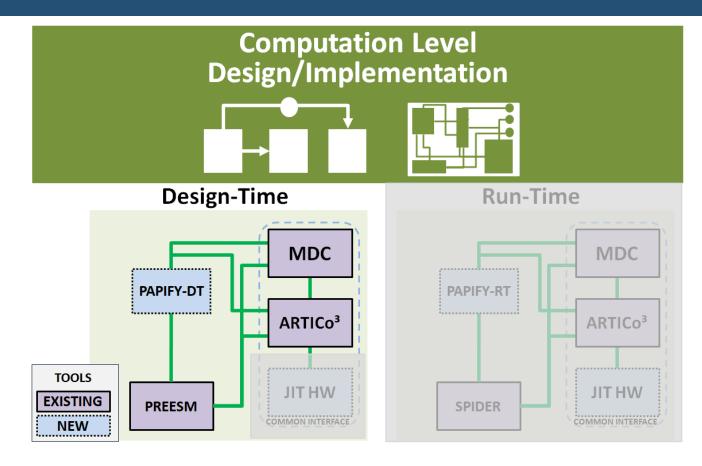

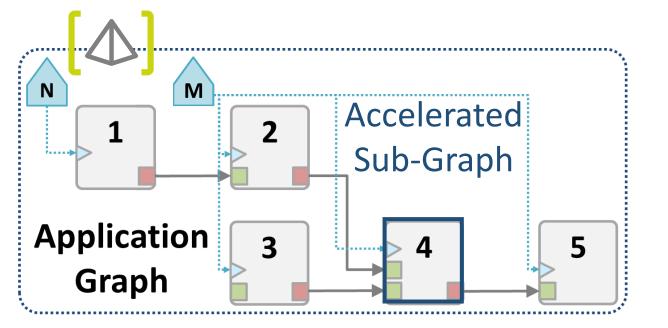

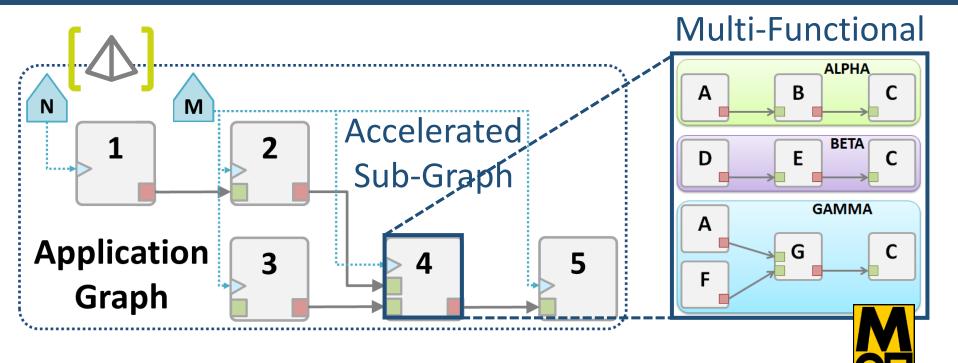

Dataflow Application

- Heterogeneity

- Adaptivity

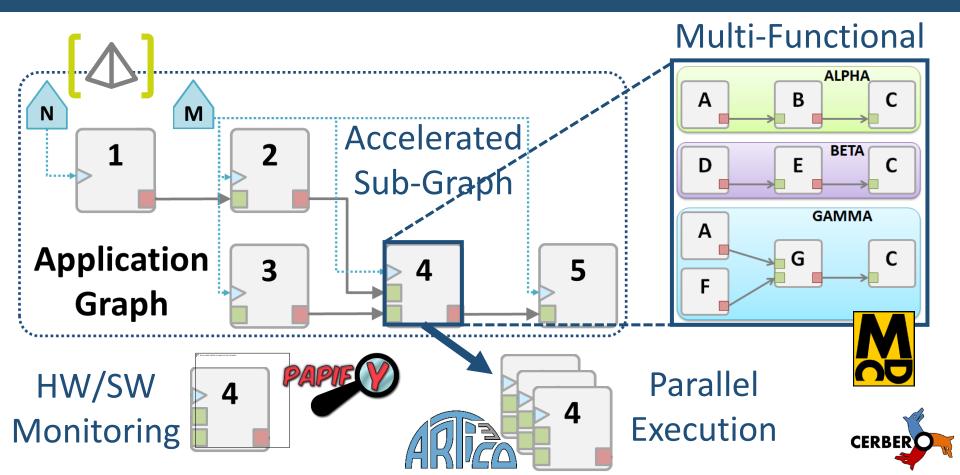

• Parallel SW Code Generation and Mapping

Parallel SW Code

Generation and Mapping

Deployment of HW CGR

Accelerator (fast reconf.)

Parallel SW Code

Generation and Mapping

Deployment of HW CGR

Accelerator (fast reconf.)

Deployment of HW DPR

Multi-Accelerator (slow reconf., HW reuse)

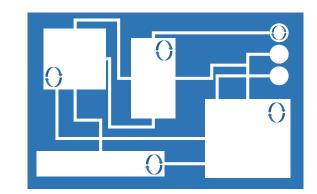

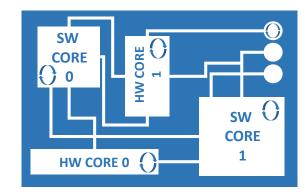

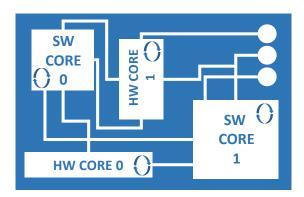

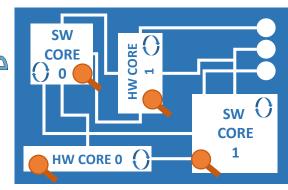

SW CORE 0 HW CORE 0

**Computing System**

- Heterogeneity

- Adaptivity

Dataflow Application

Parallel SW Code **Generation and Mapping**  Deployment of HW CGR M Accelerator (fast reconf.) Deployment of HW DPR **Multi-Accelerator (slow** reconf., HW reuse)

> Optionally with CGR inside (slow or fast reconf for Ŵ adaptation)

SW 1 CORE CORE 0 () ₹ sw O CORE 1 HW CORE 0

#### **Computing System**

- Heterogeneity

- Adaptivity

Dataflow **Application** CERBER

Parallel SW Code **Generation and Mapping**  Deployment of HW CGR M Accelerator (fast reconf.) Deployment of HW DPR **Multi-Accelerator (slow** reconf., HW reuse)

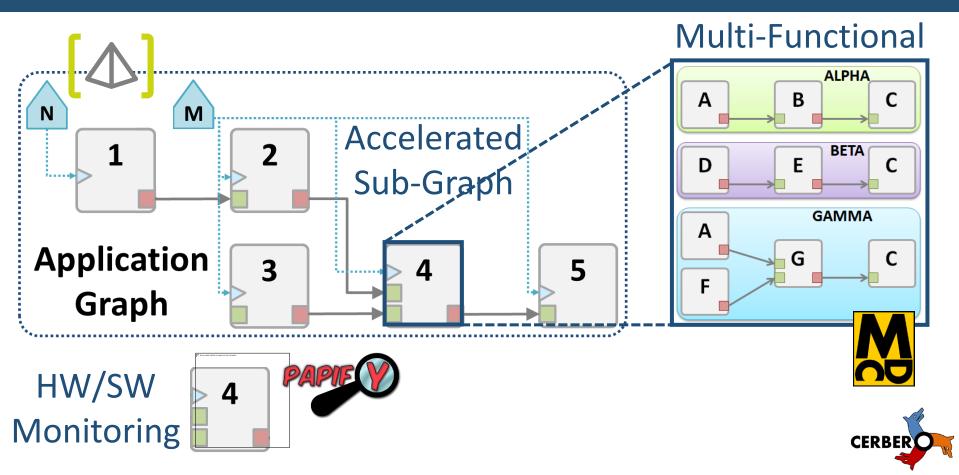

- Optionally with CGR inside (slow or fast reconf for Ŵ adaptation)

- Instrumentation for monitoring

#### **Computing System**

- Heterogeneity

- Adaptivity

Dataflow **Application** CERBER

Parallel SW Code

Generation and Mapping

Deployment of HW CGR

Accelerator (fast reconf.)

Deployment of HW DPR

Multi-Accelerator (slow reconf., HW reuse)

- Optionally with CGR inside (slow or fast reconf for adaptation)

- Instrumentation for

• Run-time management and self-adaptation (not covered in the tutorial)

#### **Computing System**

- Heterogeneity

- Adaptivity

Dataflow Application

### **CERBERO Framework – Self-Adaptive System Design**

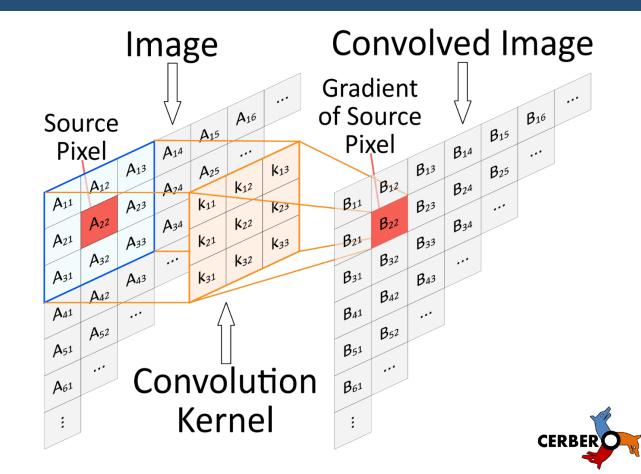

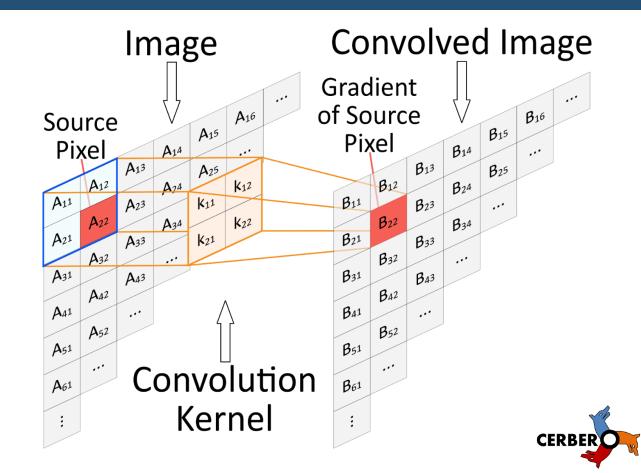

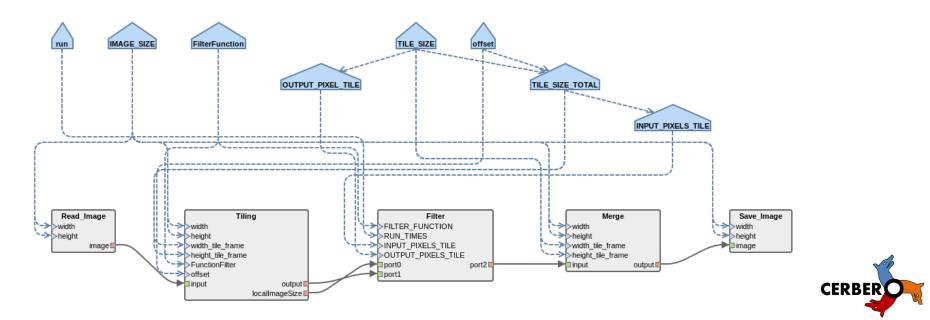

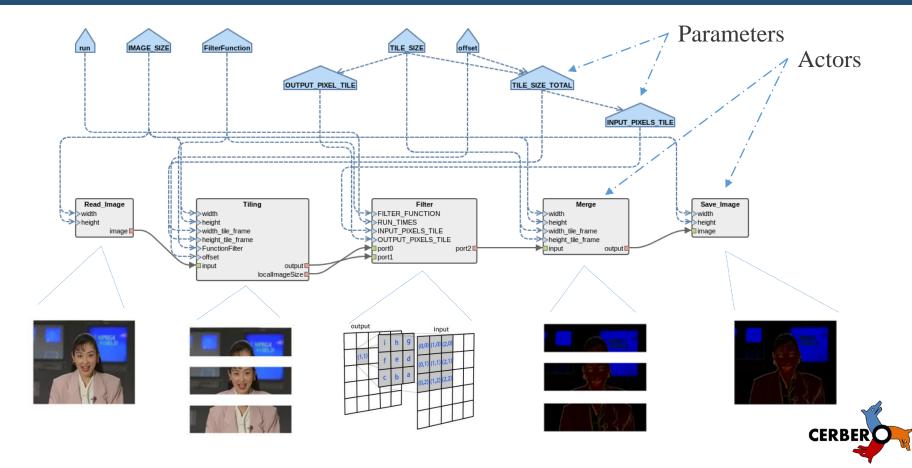

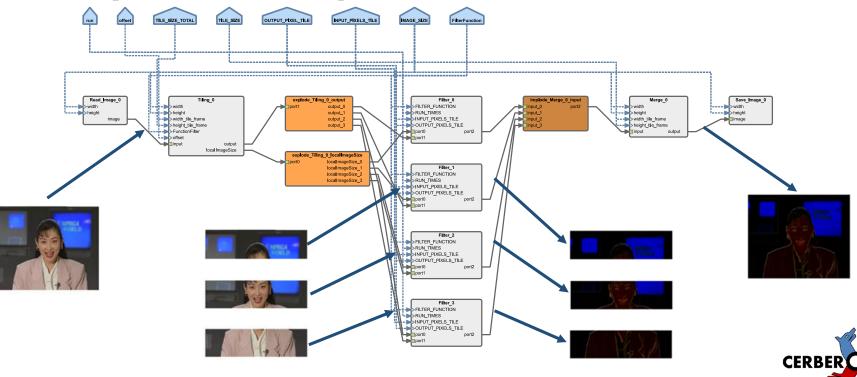

### **Tutorial Use Case**

**Sobel Operator**

$\mathbf{G}=\sqrt{{\mathbf{G}_x}^2+{\mathbf{G}_y}^2}$

$$\mathbf{G}_x = egin{bmatrix} +1 & 0 & -1 \ +2 & 0 & -2 \ +1 & 0 & -1 \end{bmatrix} \ \mathbf{G}_y = egin{bmatrix} +1 & +2 & +1 \ 0 & 0 & 0 \ -1 & -2 & -1 \end{bmatrix}$$

### **Tutorial Use Case**

**Roberts Operator**

$$\mathbf{G}=\sqrt{{\mathbf{G}_x}^2+{\mathbf{G}_y}^2}$$

$$G_x = egin{bmatrix} 0 & +1 \ -1 & 0 \end{bmatrix} \ G_y = egin{bmatrix} +1 & 0 \ 0 & -1 \end{bmatrix}$$

HiPEAC 2020 20-22 January, 2020, Bologna, Italy

### Hardware/Software Model-Based Design for Design Space Exploration and Code Generation

Horizon 2020 European Union funding for Research & Innovation

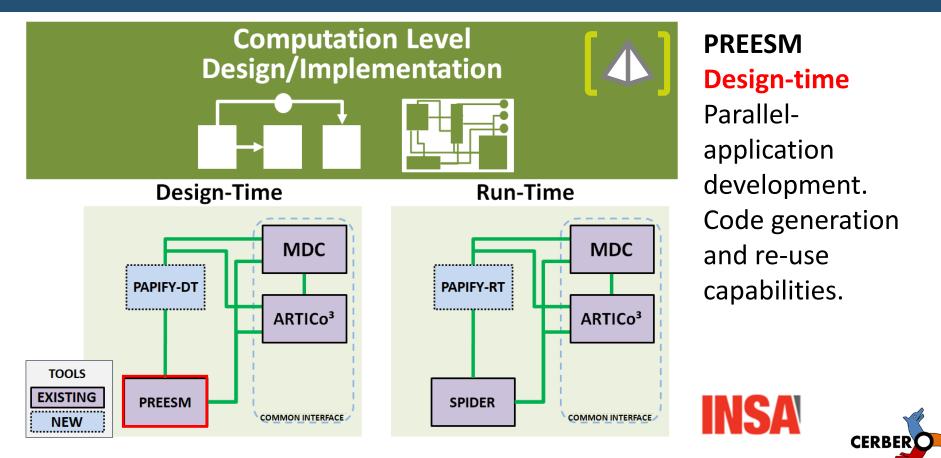

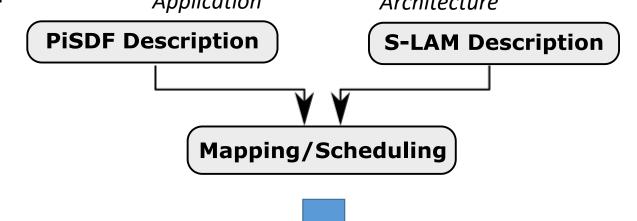

## PREESM

• Y co-design approach: keep architecture and application separate. Application Architecture

#### **AUTOMATIC CODE GENERATION for RAPID PROTOTYPING**

## PREESM

• Y co-design approach: keep architecture and application separate.

#### AUTOMATIC CODE GENERATION for RAPID PROTOTYPING

## PREESM

• Y co-design approach: keep architecture and application separate.

AUTOMATIC CODE GENERATION for RAPID PROTOTYPING for MPSoCs (CPUs + FPGA)

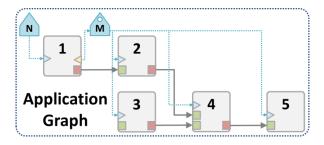

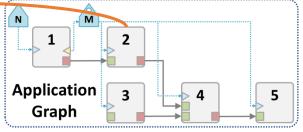

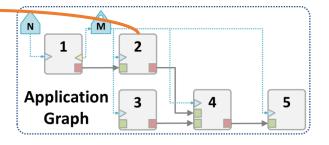

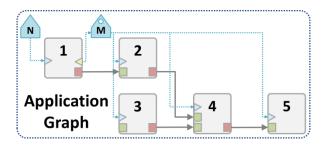

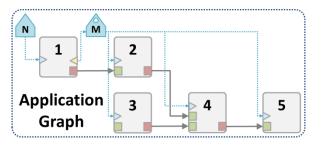

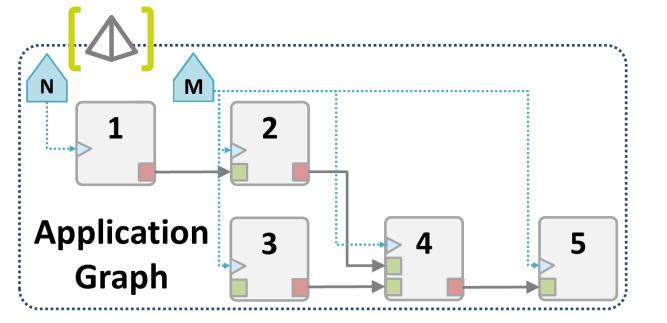

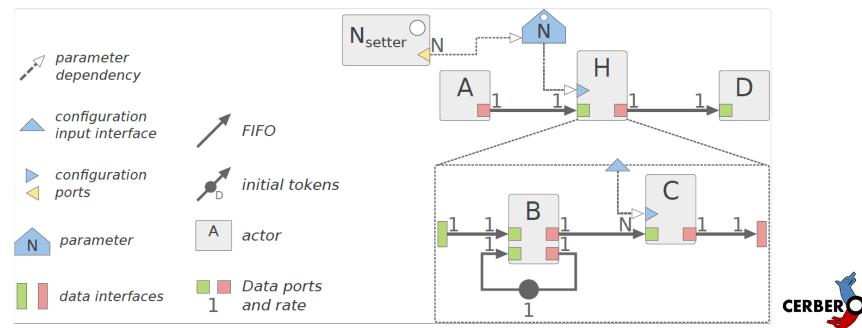

## **PiSDF: Parameterized and Interfaced SDF**

#### • Semantics:

## **PiSDF: Parameterized and Interfaced SDF**

• Application :

# **Actor Specification**

# **Exposed Parallelism**

**Equivalent single-rate graph** where each edge has equal production and consumption rates of token.

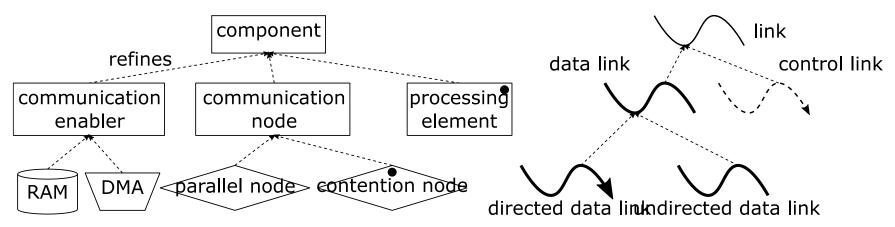

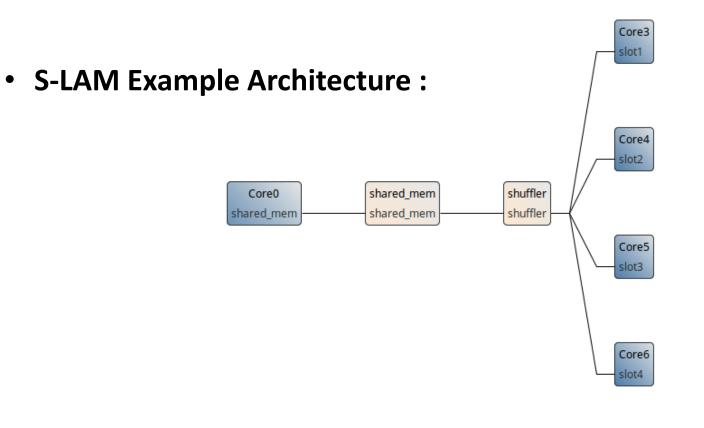

## S-LAM: System-Level Architecture Model

• S-LAM typology:

## **S-LAM: System-Level Architecture Model**

# **PREESM Mapping and Scheduling**

| Xubuntu_1 [Running] - Oracle VM VirtualBox  |                |                                                                                 |                                |                |                  |          |             |           |              |         |           |           |             | 000    |          |  |  |  |  |  |  |  |  |  |  |  |  |

|---------------------------------------------|----------------|---------------------------------------------------------------------------------|--------------------------------|----------------|------------------|----------|-------------|-----------|--------------|---------|-----------|-----------|-------------|--------|----------|--|--|--|--|--|--|--|--|--|--|--|--|

| File Machine View Input Devices Help        |                |                                                                                 |                                |                |                  |          |             |           |              |         |           |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

| •                                           |                |                                                                                 |                                | workspace - In | plementation - F | reesm    |             |           |              |         |           |           |             |        | - + ×    |  |  |  |  |  |  |  |  |  |  |  |  |

| File Edit Navigate Search Project Run Windo | W H            | elp                                                                             |                                |                |                  |          |             |           |              |         |           |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

| 📑 🕶 🔚 🐚 📮 🔅 🕶 💽 🕶 💁 🖝 🍐                     | 🔗 🔻            | ₽ -                                                                             | } <b>- ∜</b> > ♦               | • 🗘 •          |                  |          |             |           |              |         |           | Q         | uick Access | ]   🖻  |          |  |  |  |  |  |  |  |  |  |  |  |  |

| ြာ Project Explorer 🕴 📄 🔄 🔽 🔍 🗖             | [6] L          | (하) Latency:1032963 Cost:1263742 20:26:16 [ふ] Latency:1730 Cost:1916 20:26:31 않 |                                |                |                  |          |             |           |              |         |           |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

| ▼ 1 tutorialSummerSchoolFixedTile           | Solution Gantt |                                                                                 |                                |                |                  |          |             |           |              |         |           |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

| 🕨 🗁 Algo                                    |                | Time                                                                            |                                |                |                  |          |             |           |              |         |           |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

| 🕨 🗁 Archi                                   |                |                                                                                 | 0 cycles                       | 250 cycles     | 500 cyc          | es       | 750 cycl    |           | 1000 cycles  | 125     | 0 cycles  | 150       | 0 cycles    | 175    | 0 cycles |  |  |  |  |  |  |  |  |  |  |  |  |

| Code                                        |                |                                                                                 |                                |                |                  |          |             |           |              |         |           |           |             | -      |          |  |  |  |  |  |  |  |  |  |  |  |  |

| Constant     Constant     Constant          |                | Core0                                                                           | Read_ T                        | iling Filter   | Filter Filter    | Filter   | ilterFilte  | Filter    | Filter Filte | Filter  | FilterFi  | lterFil   | ter Merg    | € Save |          |  |  |  |  |  |  |  |  |  |  |  |  |

| SDF                                         |                | Slot1 -                                                                         |                                | Filter         | Filter Filter    | FilterF  | ilter Filte | er Filter | Filter Filte | Filter  | Filter Fi | ilter Fil | ter         |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

| ▼ ⊖ Workflows                               | 2              | SIDU                                                                            |                                |                | ا بسالس          |          |             |           |              |         | ويسب      |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

| I∕⁄⁄ Codegen.workflow                       | rato           | Slot2 -                                                                         |                                | Filter         | Filter Filter I  | Filter F | ilter Filte | r Filter  | Filter Filte | Filter  | Filter Fi | ilter Fil | ter         |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

|                                             | Operators      | 0-+0                                                                            |                                | Eilter         | Filter Filter    | Filter F | ilter Eilte | Filter    | Eilter Eilte | Filter  | Eilter Ei | ilter Fil | ter         |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

|                                             |                | Slot3 -                                                                         |                                |                |                  |          |             |           |              |         |           |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

| Be Outline 🛛 🗖 🗖                            |                | Slot4                                                                           |                                | Filter         | Filter Filter    | Filter F | ilter Filte | er Filter | Filter Filte | Filter  | Filter Fi | ilter     |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

| An outline is not available.                |                |                                                                                 |                                |                |                  |          |             |           |              |         |           |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

|                                             | Gan            | Santt Loads Work, Span and Achieved Speedup                                     |                                |                |                  |          |             |           |              |         |           |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

|                                             | P              | 🛛 Properties 🧔 Tasks 🔝 Problems 📮 Console 🕱                                     |                                |                |                  |          |             |           |              |         | B. 🔠      | ₽ .       | . 🖻 🗕 🕻     | 9 🗸    |          |  |  |  |  |  |  |  |  |  |  |  |  |

|                                             | DFTo           | ols Workf                                                                       | ow console                     |                |                  |          |             |           |              |         |           |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

|                                             |                |                                                                                 | OTICE: [HARDW<br>OTICE: [HARDW |                |                  |          |             | d defin   | itions.      |         |           |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

|                                             | 20:2           | 26:32 N                                                                         | OTICE: [HARDW                  | ARE] number    | of OutputDa      |          |             | erted is  | 51           |         |           |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

|                                             |                |                                                                                 | OTICE: [HARDW<br>OTICE: [HARDW |                |                  | o nroP   | rocessing   |           |              |         |           |           |             |        | 0        |  |  |  |  |  |  |  |  |  |  |  |  |

|                                             |                |                                                                                 | OTICE: Workfl                  |                |                  |          |             |           | ixedTile/Wo  | rkflows | /Codeger  | n.workt   | low.        |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

|                                             |                |                                                                                 |                                |                |                  |          |             |           |              |         |           |           |             |        | U        |  |  |  |  |  |  |  |  |  |  |  |  |

|                                             | ДС             |                                                                                 |                                |                |                  |          |             |           |              |         |           |           |             |        |          |  |  |  |  |  |  |  |  |  |  |  |  |

HiPEAC 2020 20-22 January, 2020, Bologna, Italy

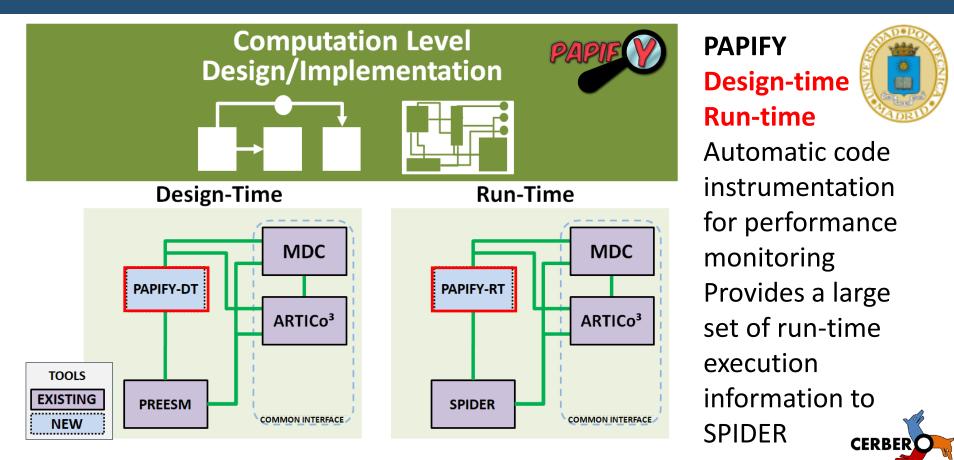

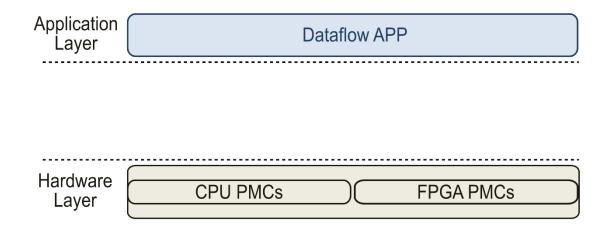

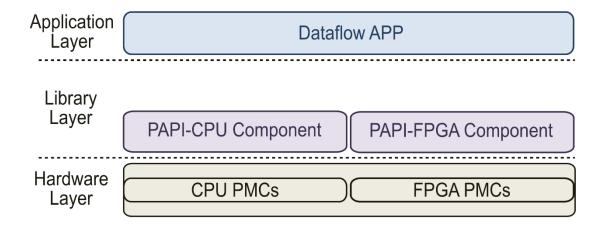

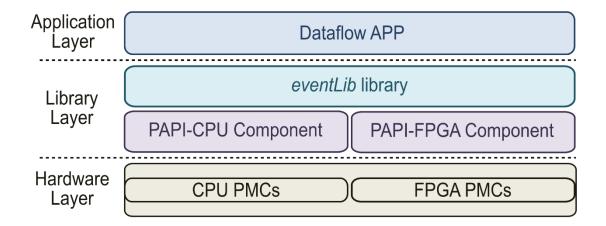

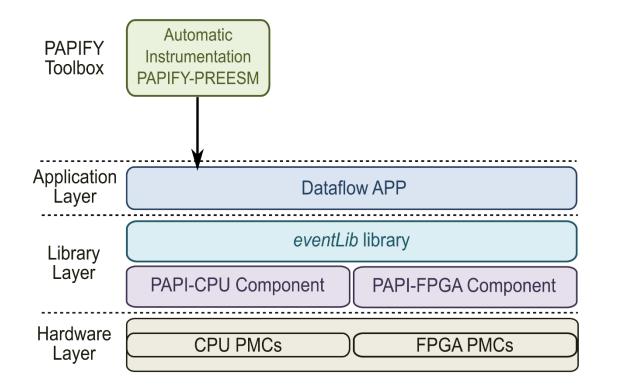

## **System Performance Monitoring**

Horizon 2020 European Union funding for Research & Innovation

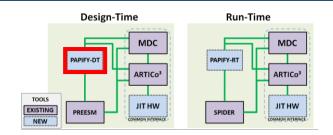

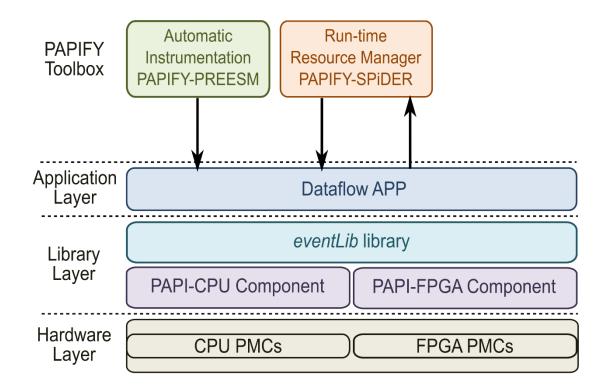

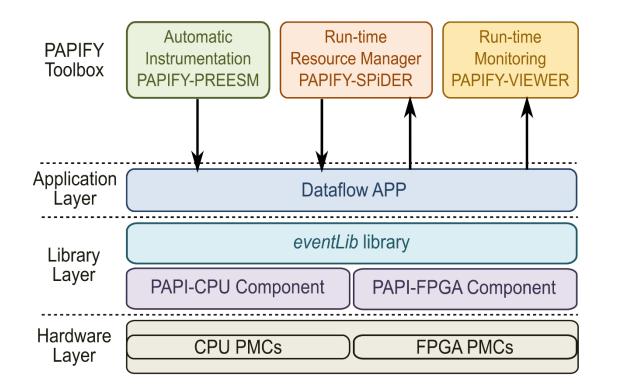

### **CERBERO Monitoring: PAPIFY**

### **CERBERO Monitoring: PAPIFY**

### **CERBERO Monitoring: PAPIFY**

configure\_papify\_actor(...); configure\_papify\_PE(...);

// Configure monitoring of each actor

// Configure each PE

```

configure_papify_actor(...);

configure_papify_PE(...);

```

// Configure monitoring of each actor

// Configure each PE

actor\_execution();

. . .

// Execute the actor

```

configure papify actor(...);

configure papify PE(...);

```

// Configure monitoring of each actor // Configure each PE

```

event start(...);

// Start monitoring PAPI events

event_start_papify_timing(...); // Start monitoring timing

```

```

actor execution();

```

. . .

```

// Execute the actor

```

```

event_events(...);

event_stop_papify_timing(...); // Stop monitoring timing

event write file(...);

```

```

// Stop monitoring PAPI events

// Dump monitoring info

```

HiPEAC 2020 20-22 January, 2020, Bologna, Italy

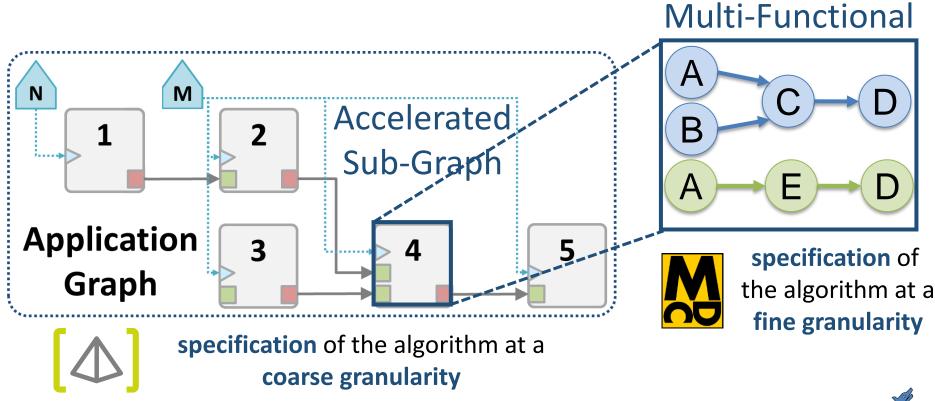

#### **Creating Hardware Accelerators with DPR and CGR**

Horizon 2020 European Union funding for Research & Innovation

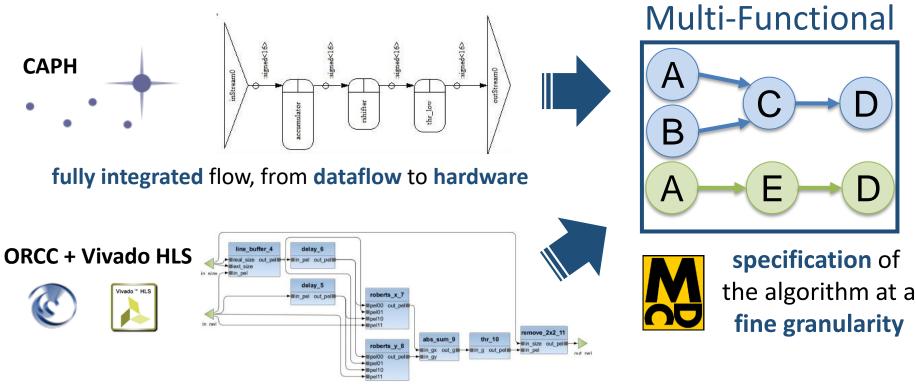

two steps flow: ORCC for dataflow network, Vivado HLS deals for actors hardware code generation

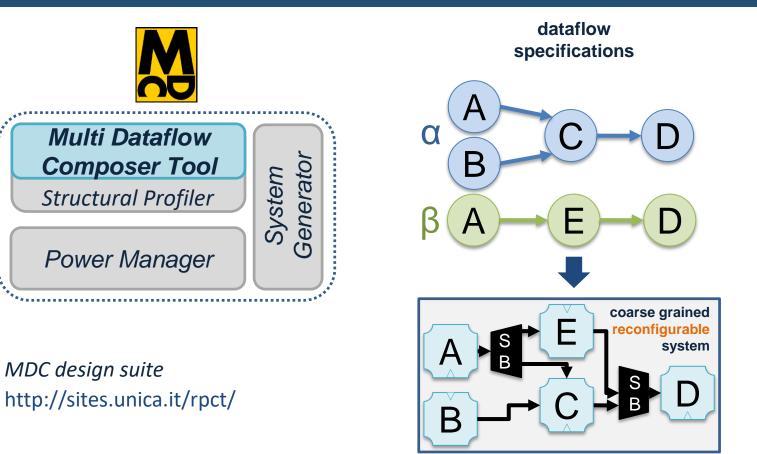

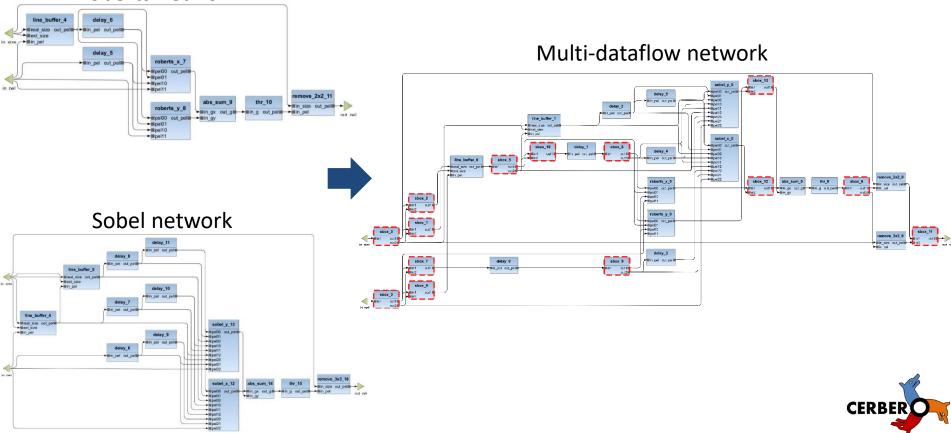

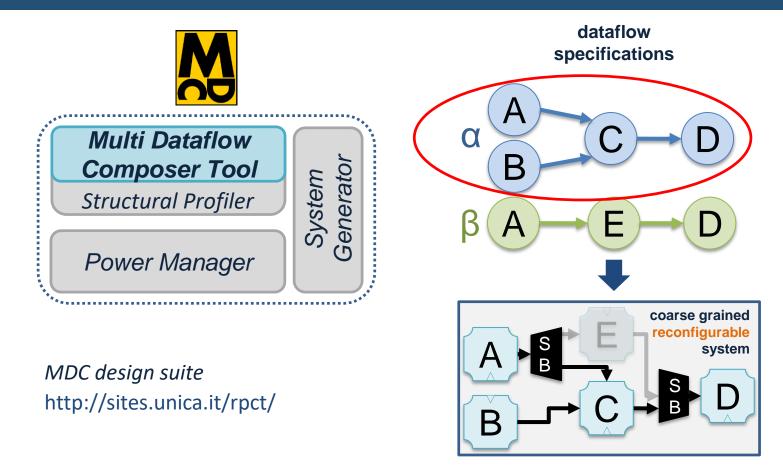

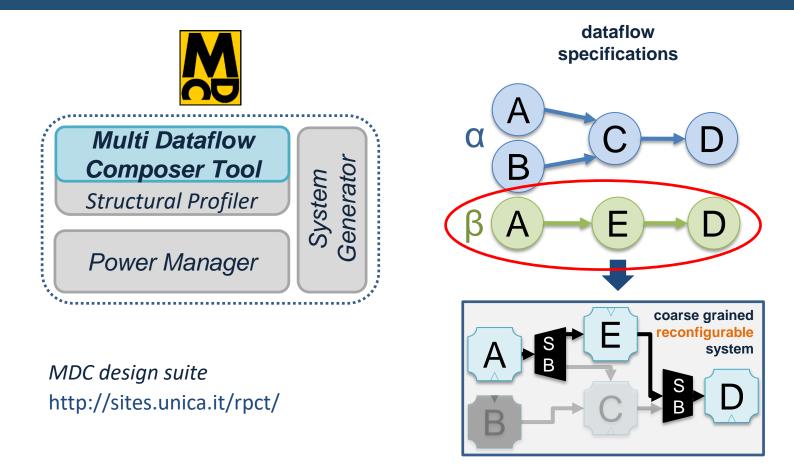

## **MDC: Merging**

**Roberts network**

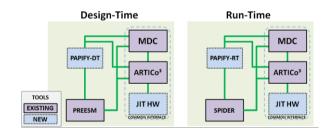

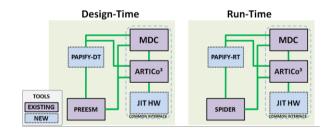

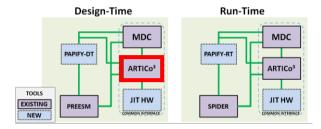

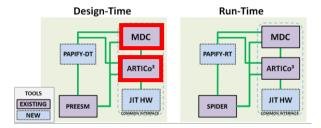

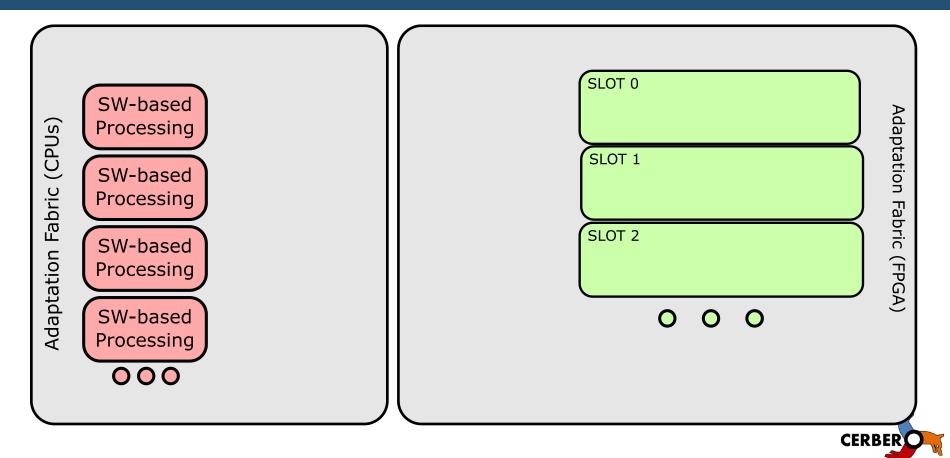

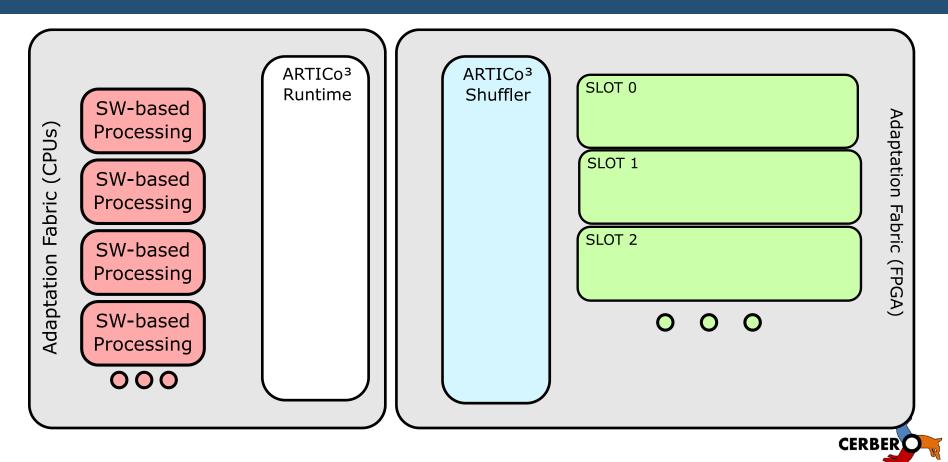

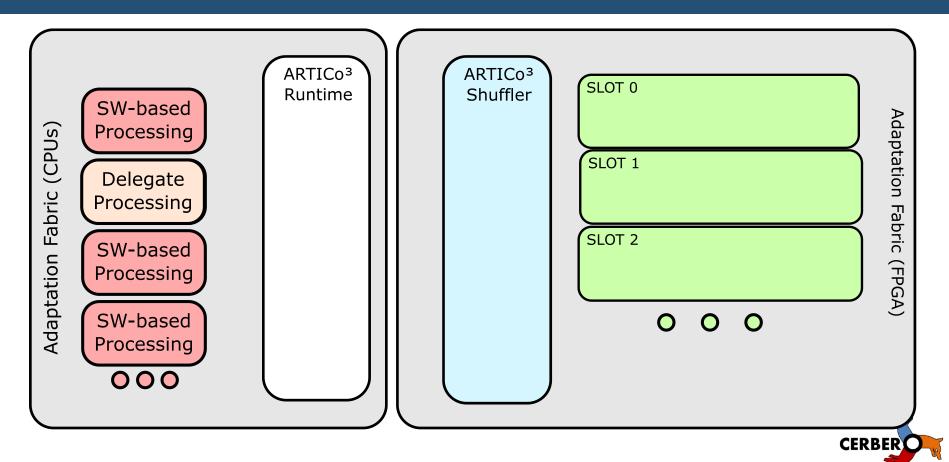

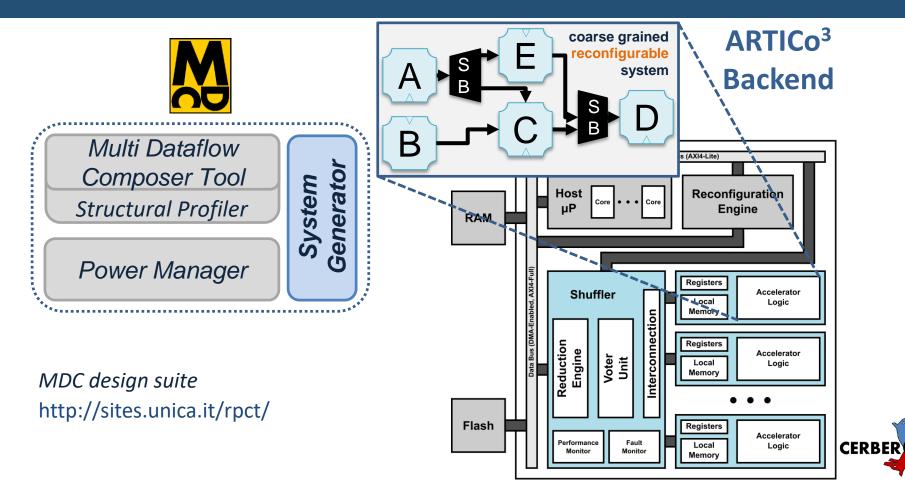

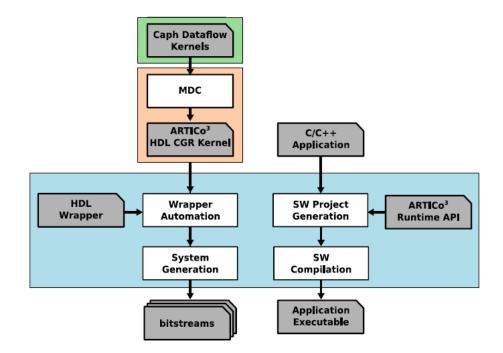

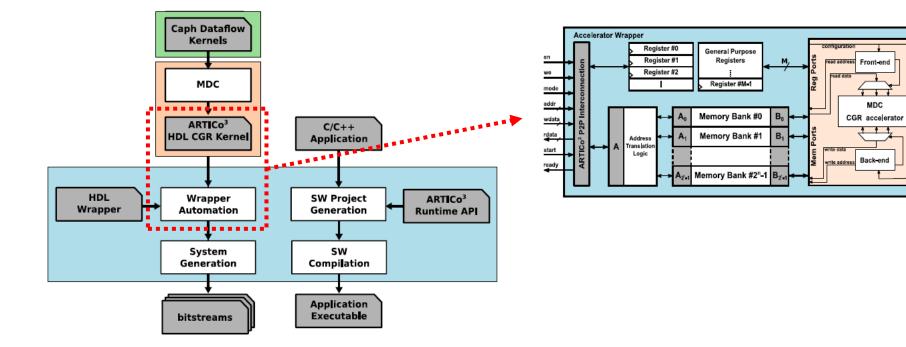

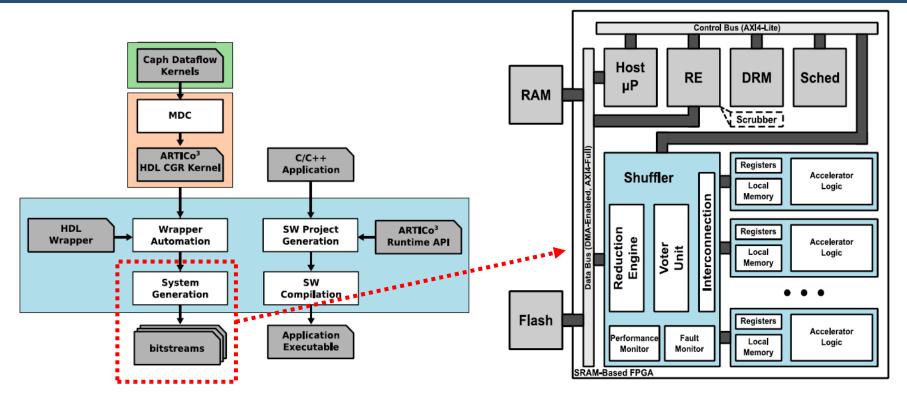

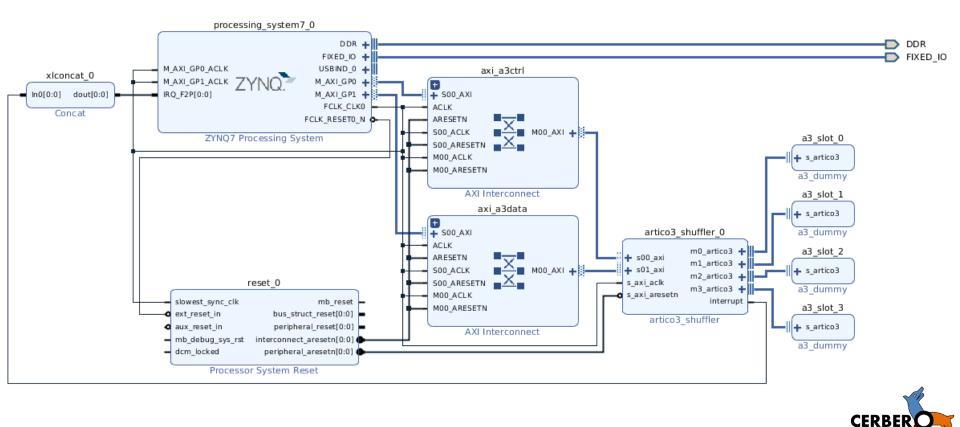

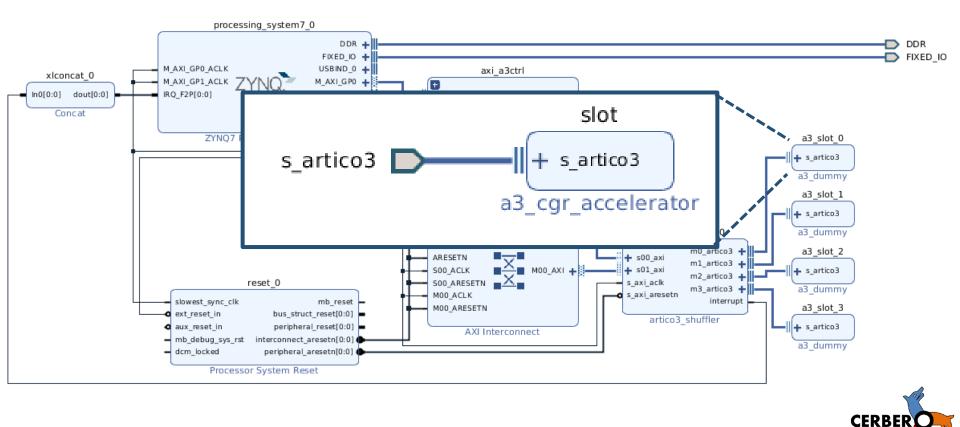

## **ARTICo<sup>3</sup>** Design Flow

# **ARTICo<sup>3</sup>** Design Flow

## **ARTICo<sup>3</sup>** Design Flow

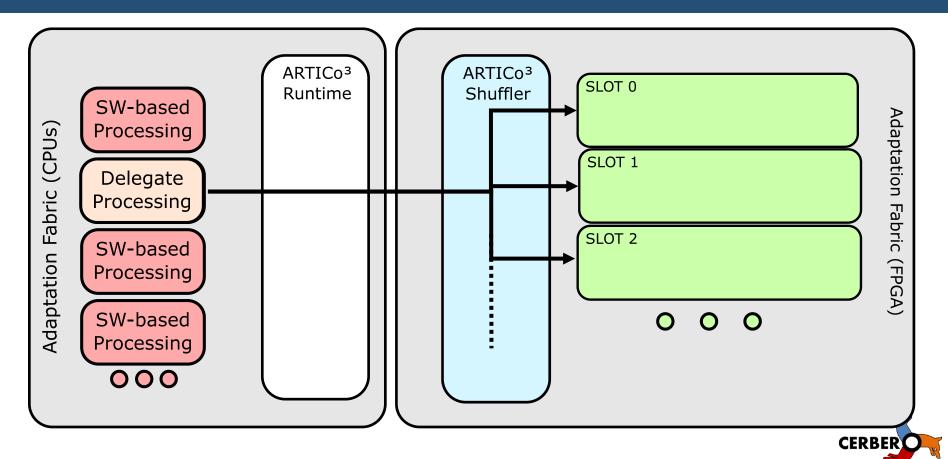

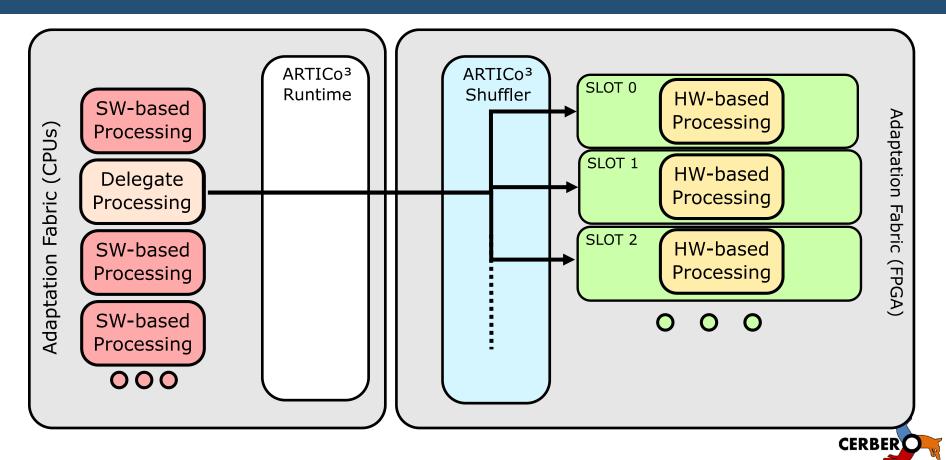

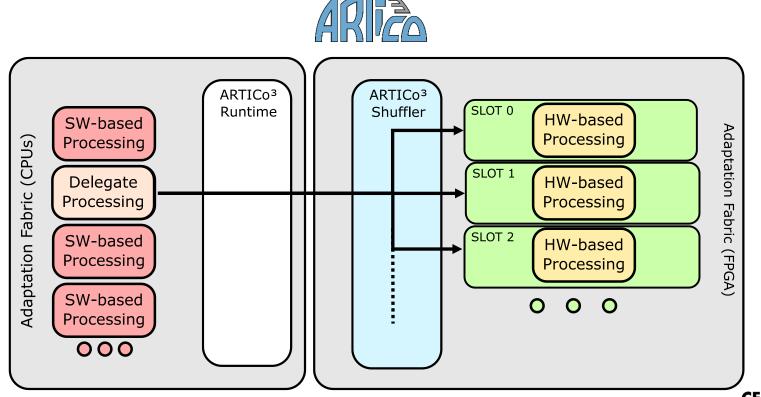

## Heterogeneous Device

CERBER

#### Architecture Overview in Vivado

#### Architecture Overview in Vivado

HiPEAC 2020 20-22 January, 2020, Bologna, Italy

#### CERBERO H2020 Project – Tutorial: Design Flow for Heterogeneous Embedded Computing Infrastructures

Horizon 2020 European Union funding for Research & Innovation

## **Additional Slides**