# Platform-Agnostic Dataflow-to-Hardware Design Flow for Reconfigurable Systems

Francesca Palumbo<sup>1</sup>, Claudio Rubattu<sup>1,2</sup>, **Carlo Sau<sup>3</sup>**, Luigi Raffo<sup>3</sup> and Maxime Pelcat<sup>2</sup>

<sup>1</sup>University of Sassari, IDEA Lab

<sup>2</sup>University of Rennes, INSA

<sup>3</sup>University of Cagliari, DIEE, EOLAB

Naples, 20-22 June 2018

# Outline

- Introduction

- Embedded Moving Toward IoT and CPS

- Computing Architectures for Embedded Systems

- Background

- CGRA Design From Applications to Architecture

- CGRA Design Open Issues

- CGRA Composition and Management

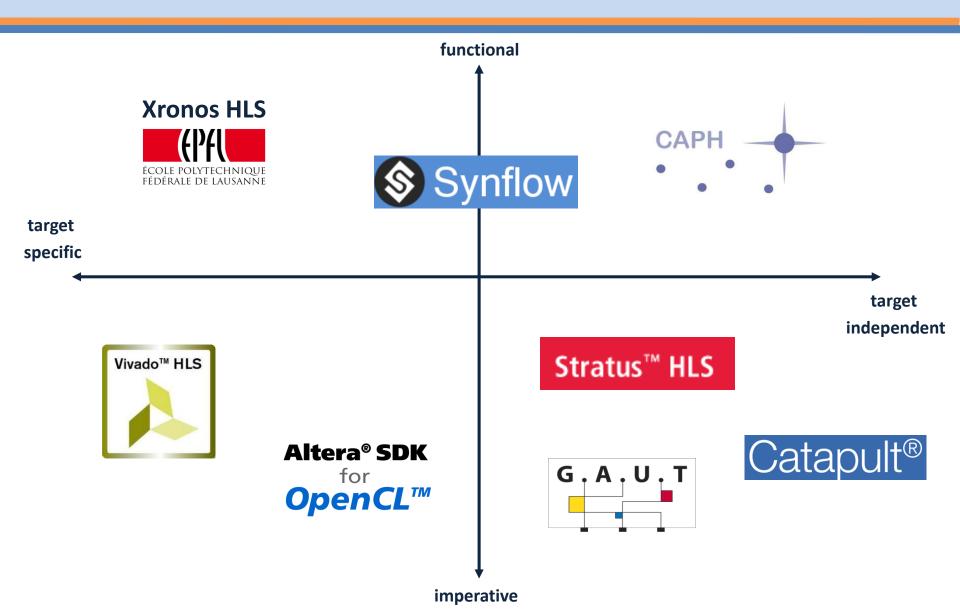

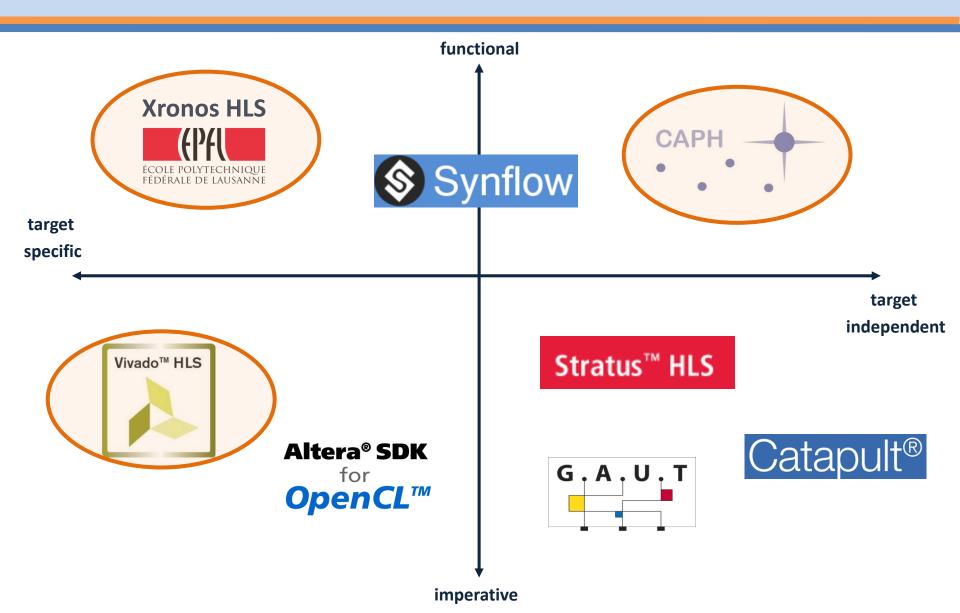

- High Level Synthesis

- Results

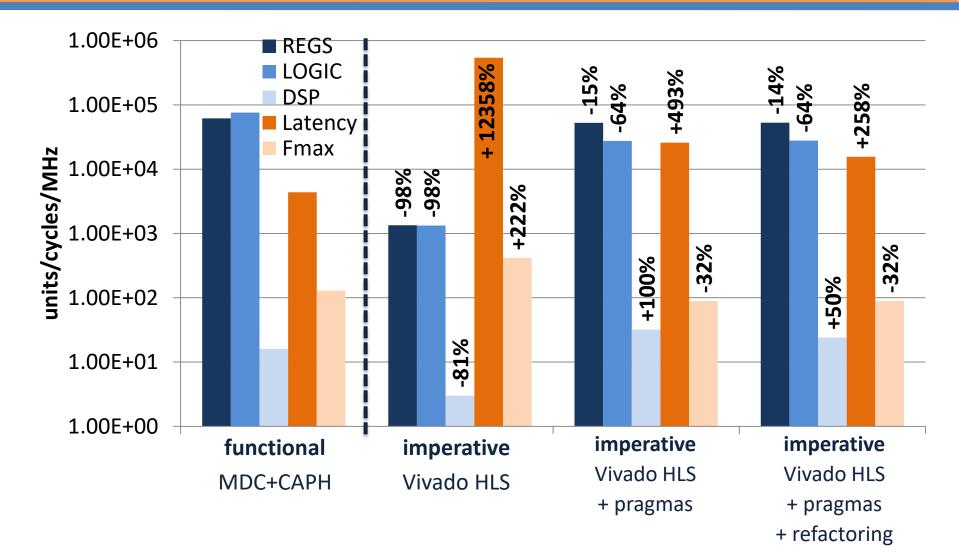

- Functional vs. Imperative HLS for CGRA

- Target Specific vs. Independent HLS for CGRA

- Final Remarks

# Outline

- Introduction

- Embedded Moving Toward IoT and CPS

- Computing Architectures for Embedded Systems

- Background

- CGRA Design From Applications to Architecture

- CGRA Design Open Issues

- CGRA Composition and Management

- High Level Synthesis

- Results

- Functional vs. Imperative HLS for CGRA

- Target Specific vs. Independent HLS for CGRA

- Final Remarks

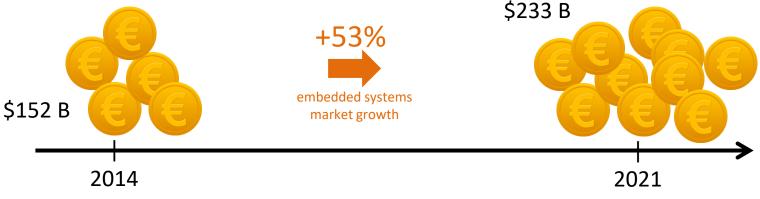

Embedded Moving Toward IoT and CPS

Embedded Systems (*real-time* computing systems with a dedicated functionality), often working in *constrained* and *portable* contexts, are pervading the market.

source: Transparency Market Research

Embedded Moving Toward IoT and CPS

Embedded Systems (*real-time* computing systems with a dedicated functionality), often working in *constrained* and *portable* contexts, are pervading the market.

HIGH PERFORMANCE required to achieve real-time behaviour. Due to the constrained environment and to the portability an EXTREME EXECUTION EFFICIENCY (RESOURCES, POWER CONSUMPTION) is mandatory.

source: Transparency Market Research

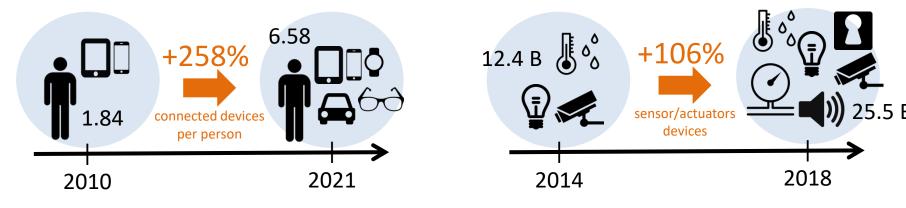

## Introduction Embedded Moving Toward IoT and CPS

Embedded Systems are becoming connected and capable of interacting with Environment, the User and the System itself, to adapt their behaviour according to changing requirements.

source: CISCO ISBG

source: IC Insights

## Introduction Embedded Moving Toward IoT and CPS

Embedded Systems are becoming connected and capable of interacting with Environment, the User and the System itself, to adapt their behaviour according to changing requirements.

Adaptivity pushes farther **FLEXIBILITY** need of the systems that have to provide several working points while, at the same time, exhibiting a **SHORT RESPONSE TIME**.

source: CISCO ISBG

source: IC Insights

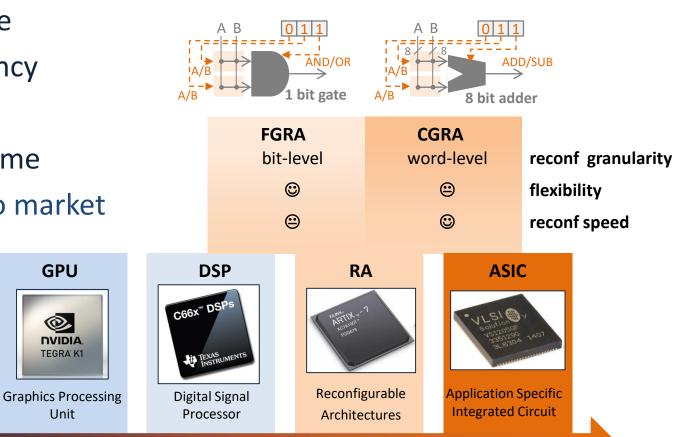

**Computing Architectures for Embedded Systems**

#### Emerging needs for modern embedded systems:

- high performance

- execution efficiency

- flexibility

- short response time

**Computing Architectures for Embedded Systems**

Emerging needs for modern embedded systems:

- high performance

- execution efficiency

- flexibility

- short response time

- minimum time to market

**Computing Architectures for Embedded Systems**

#### Emerging needs for modern embedded systems:

GPU

**DVIDIA** TEGRA K1

Unit

- high performance

- execution efficiency

- flexibility

- short response time

- minimum time to market

**CPU**

(intel)

CORPM

**Central Processing**

Unit

flexibility

performance/efficiency

**Computing Architectures for Embedded Systems**

#### Emerging needs for modern embedded systems:

GPU

©,

**DVIDIA** TEGRA K1

Unit

- high performance

- execution efficiency

- flexibility

- short response time

- minimum time to market

**CPU**

(intel) Core"

**Central Processing**

Unit

flexibility

performance/efficiency

# Outline

- Introduction

- Embedded Moving Toward IoT and CPS

- Computing Architectures for Embedded Systems

- Background

- CGRA Design From Applications to Architecture

- CGRA Design Open Issues

- CGRA Composition and Management

- High Level Synthesis

- Results

- Functional vs. Imperative HLS for CGRA

- Target Specific vs. Independent HLS for CGRA

- Final Remarks

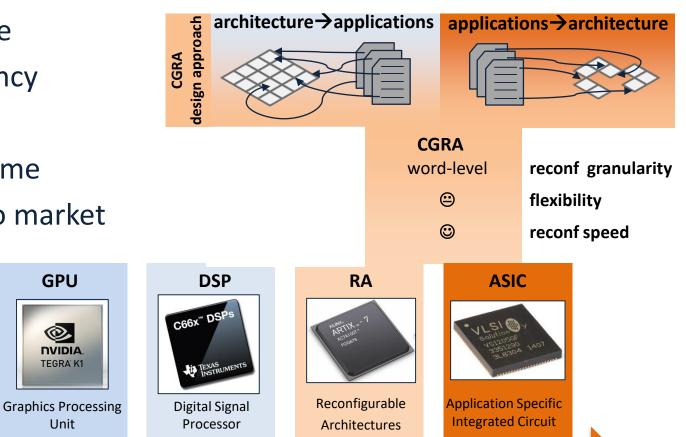

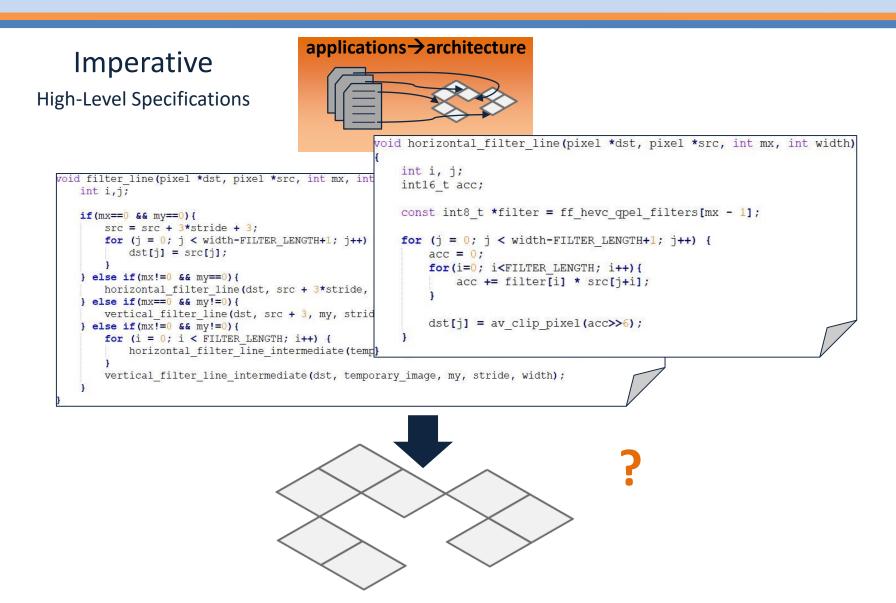

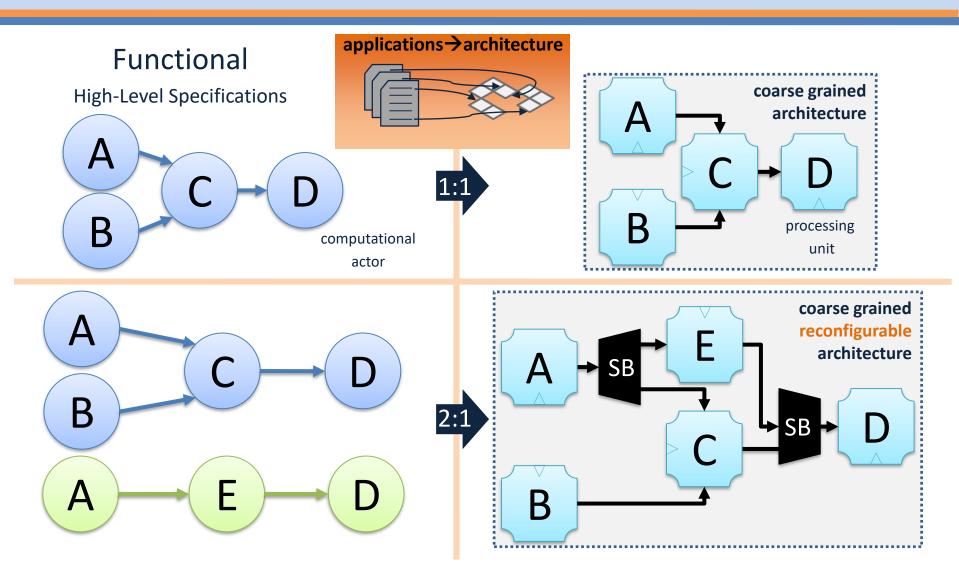

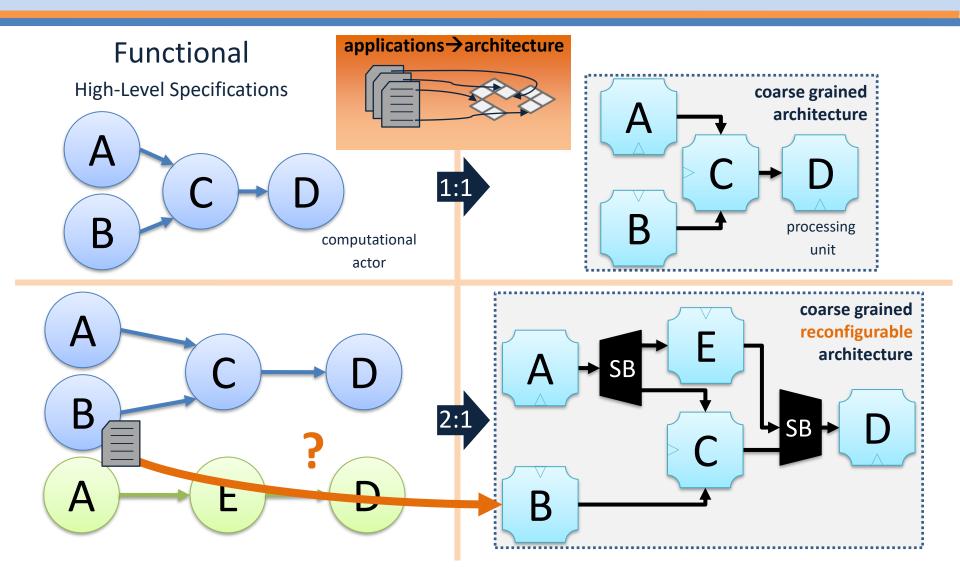

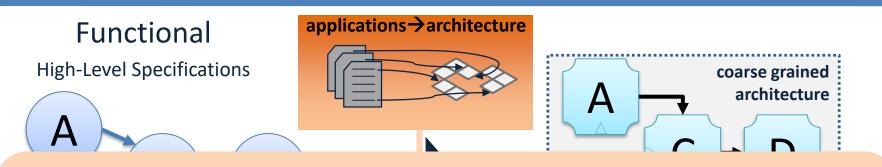

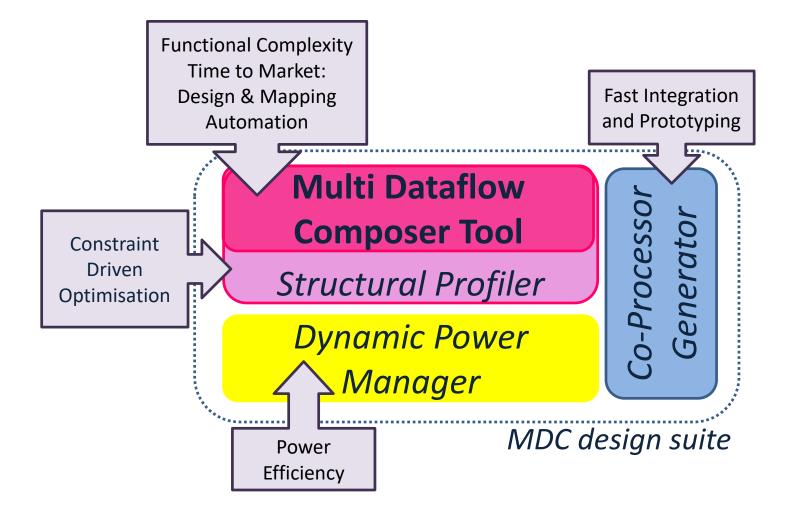

# Background

#### **CGRA** Design From Applications to Architecture

# Background

#### **CGRA** Design From Applications to Architecture

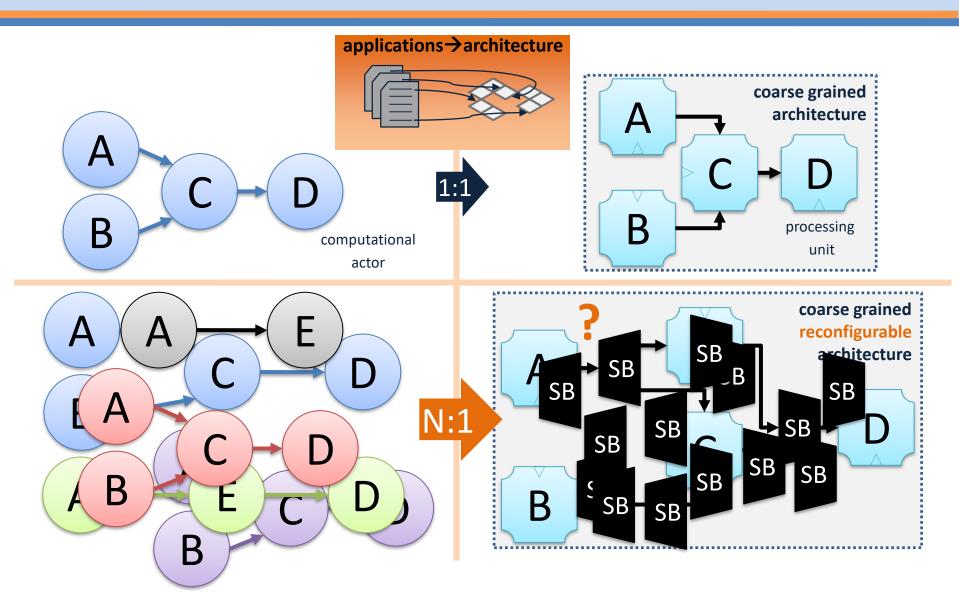

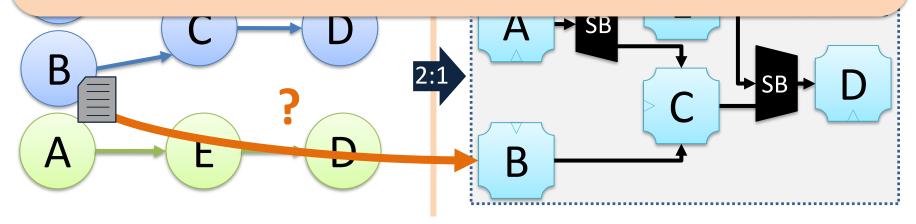

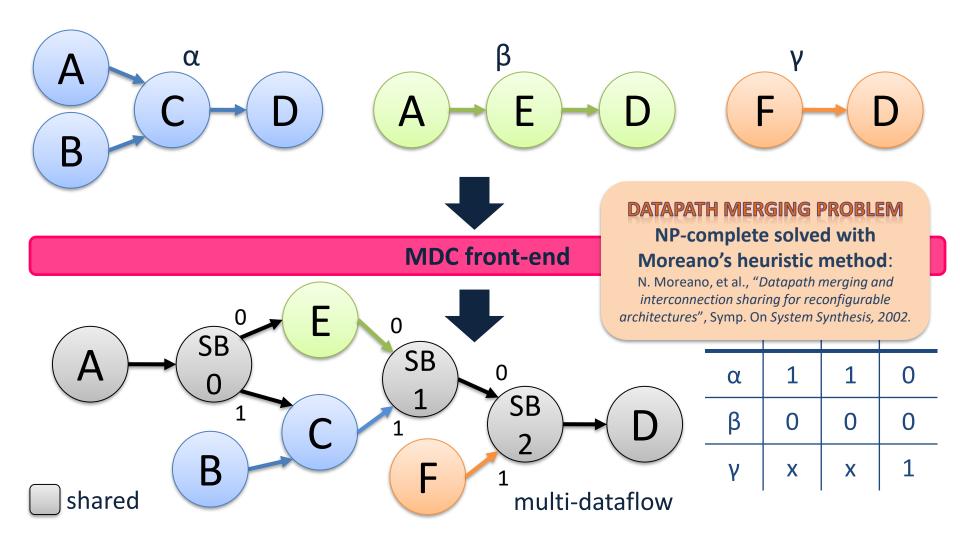

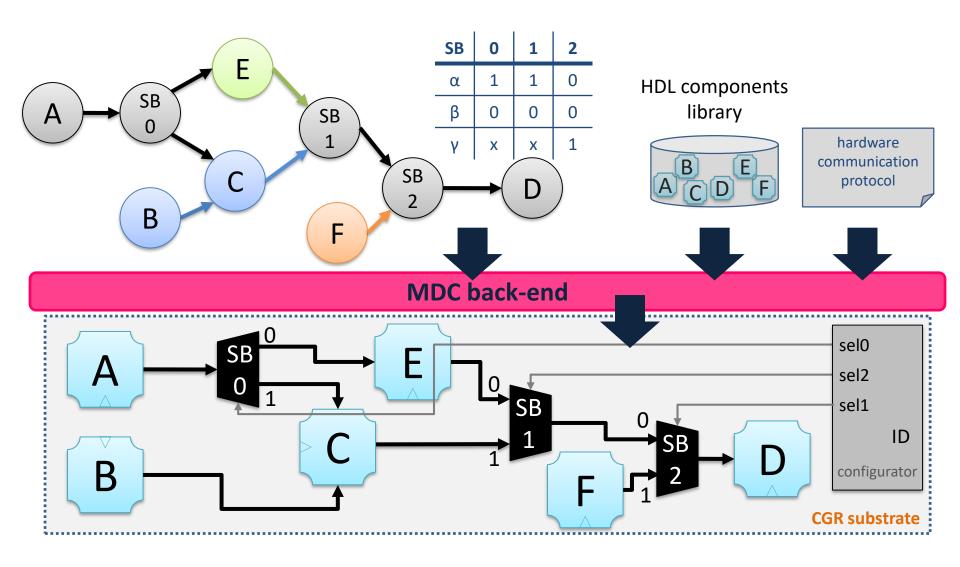

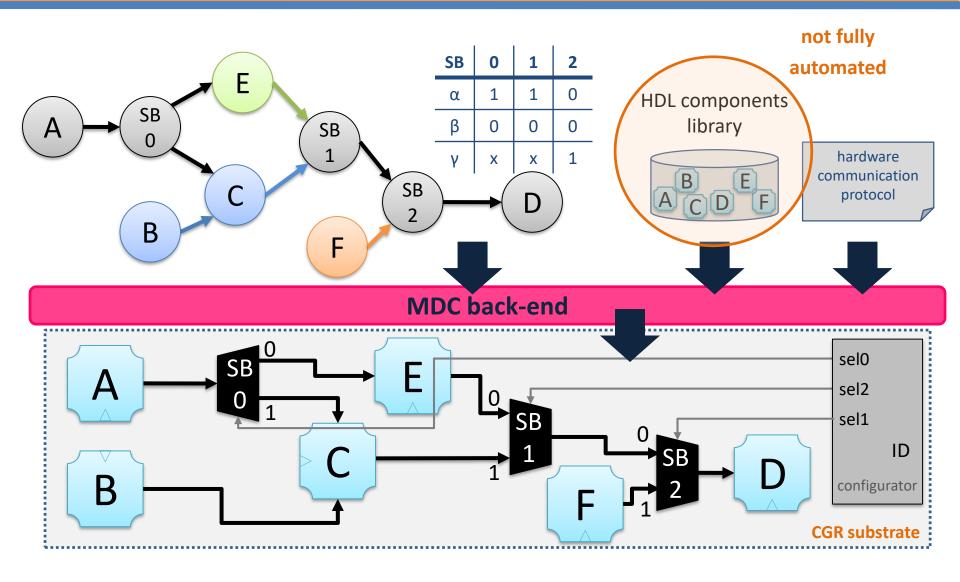

#### Background CGRA Design Open Issues

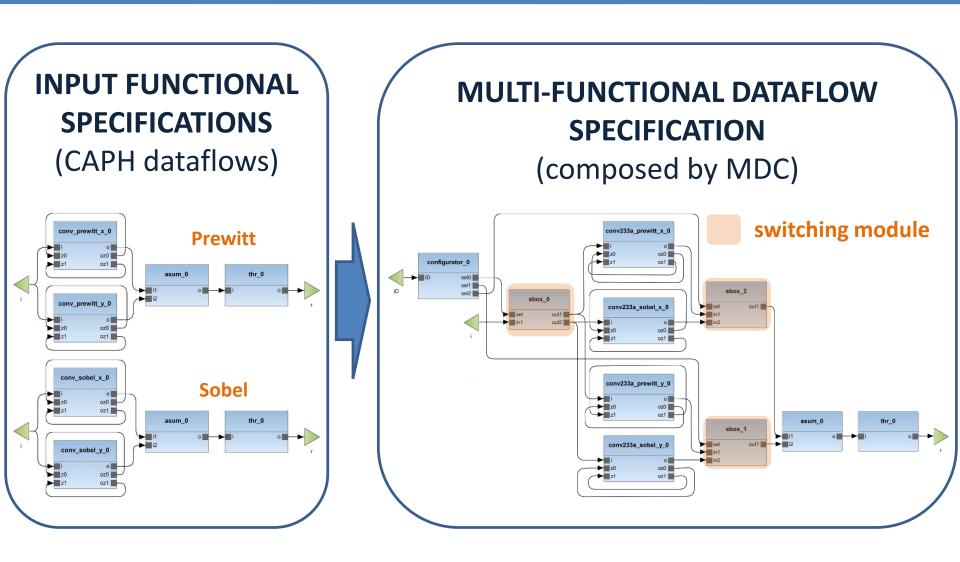

#### Background CGRA Design Open Issues

#### Background CGRA Design Open Issues

CGRA development flow requires **DESIGN AUTOMATION** to face:

- resource sharing and runtime configuration management

- high-level specification to hardware description language (HDL)

mapping

# Outline

- Introduction

- Embedded Moving Toward IoT and CPS

- Computing Architectures for Embedded Systems

- Background

- CGRA Design From Applications to Architecture

- CGRA Design Open Issues

- CGRA Composition and Management

- High Level Synthesis

- Results

- Functional vs. Imperative HLS for CGRA

- Target Specific vs. Independent HLS for CGRA

- Final Remarks

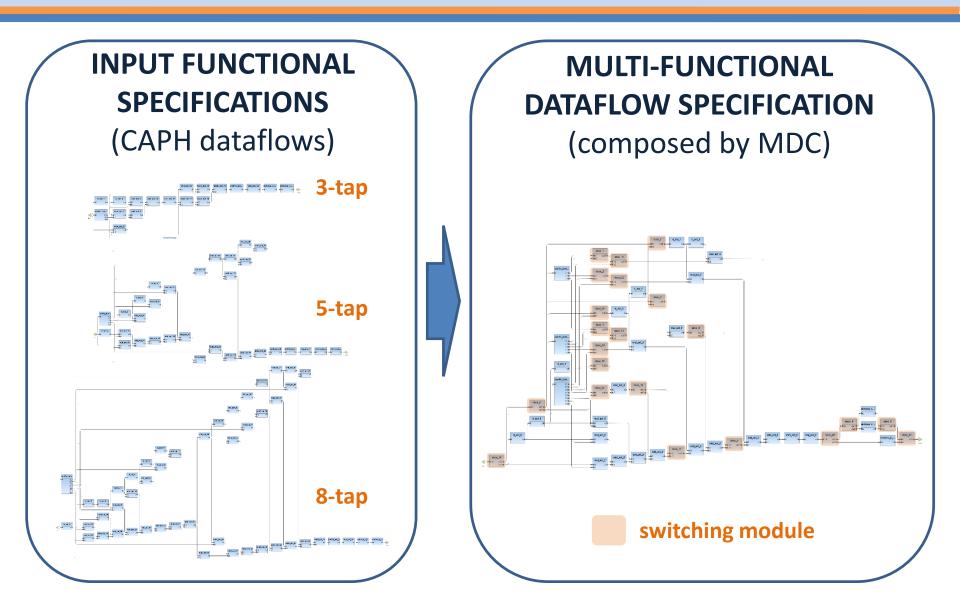

http://sites.unica.it/rpct/

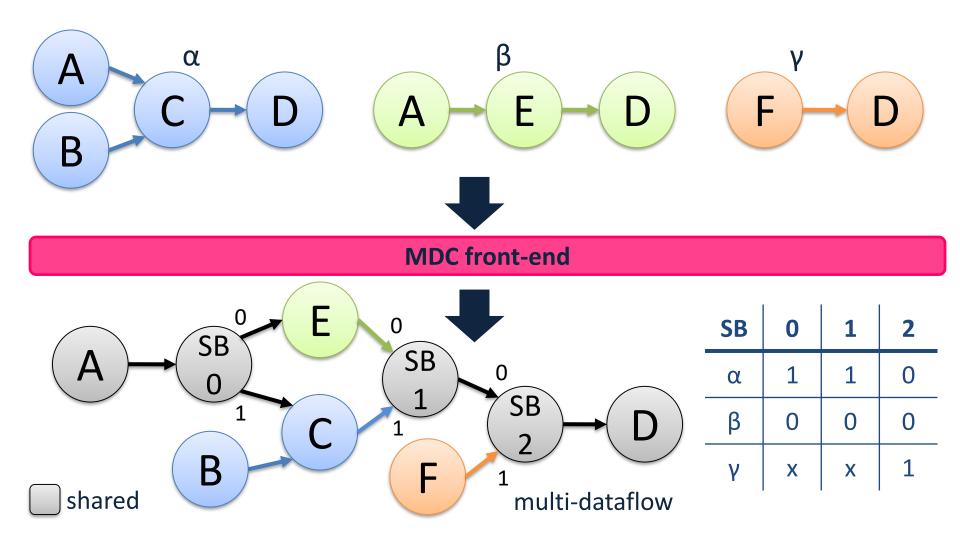

## CGRA Composition and Management High Level Synthesis

## CGRA Composition and Management High Level Synthesis

# Outline

- Introduction

- Embedded Moving Toward IoT and CPS

- Computing Architectures for Embedded Systems

- Background

- CGRA Design From Applications to Architecture

- CGRA Design Open Issues

- CGRA Composition and Management

- High Level Synthesis

- Results

- Functional vs. Imperative HLS for CGRA

- Target Specific vs. Independent HLS for CGRA

- Final Remarks

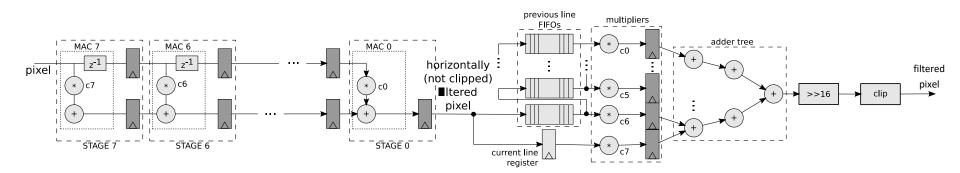

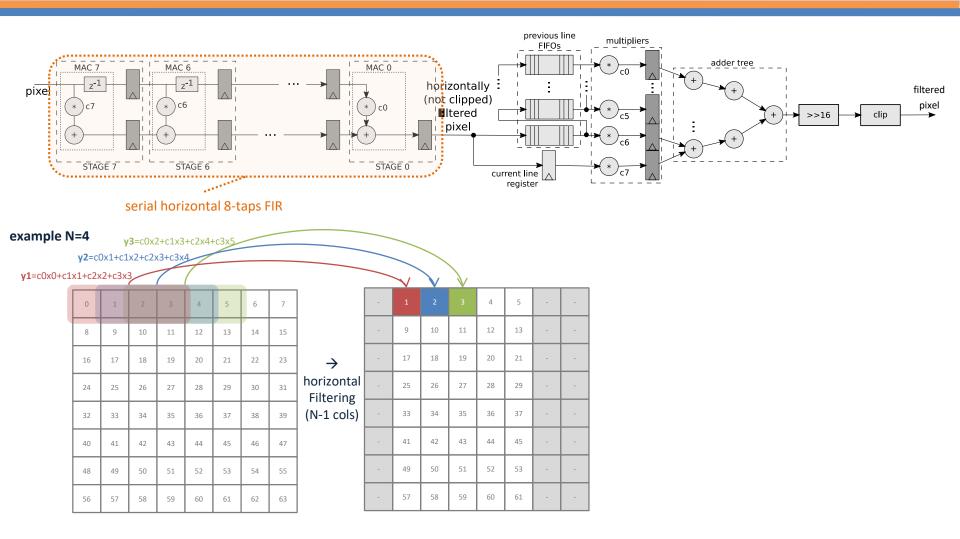

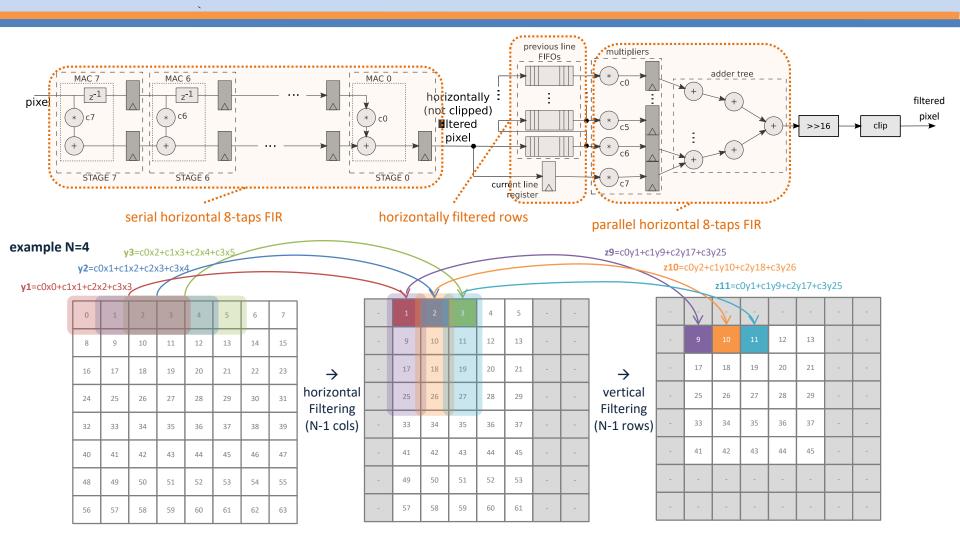

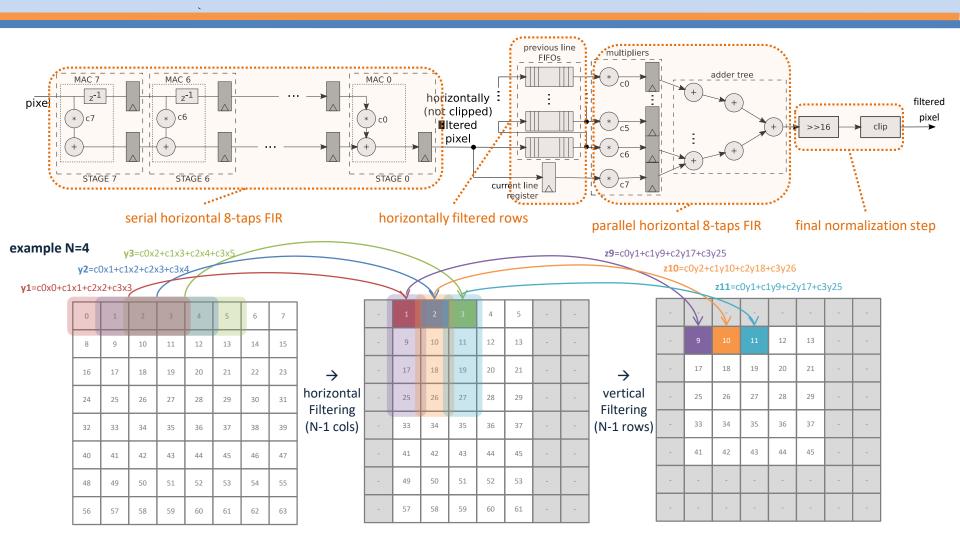

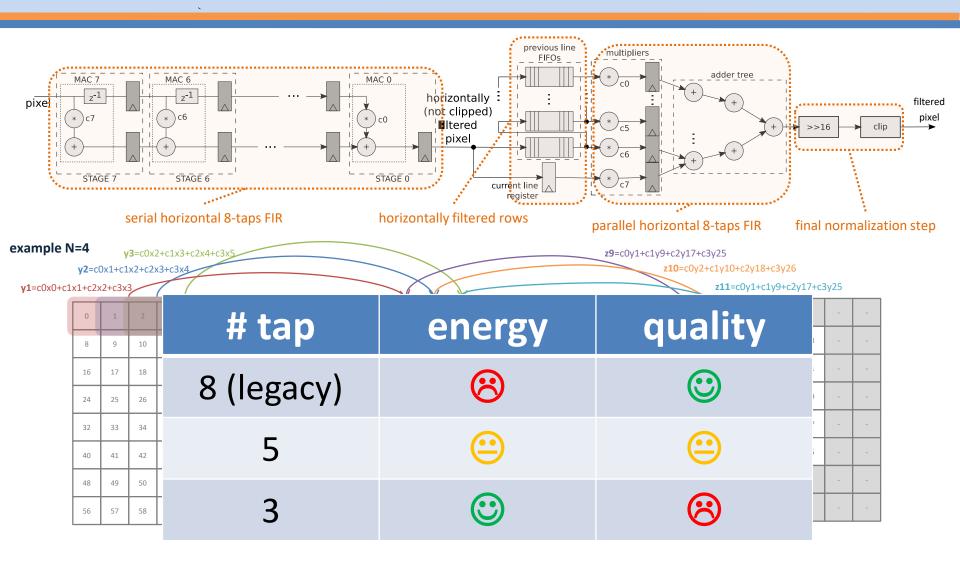

#### example N=4

| 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  |

|----|----|----|----|----|----|----|----|

| 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |

| 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 |

| 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

| 48 | 49 | 50 | 51 | 52 | 53 | 54 | 55 |

| 56 | 57 | 58 | 59 | 60 | 61 | 62 | 63 |

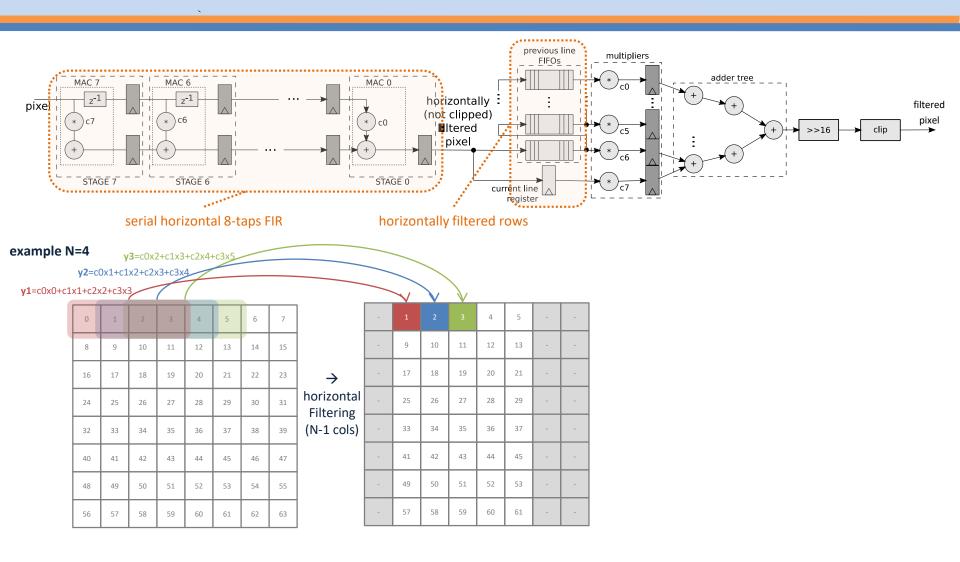

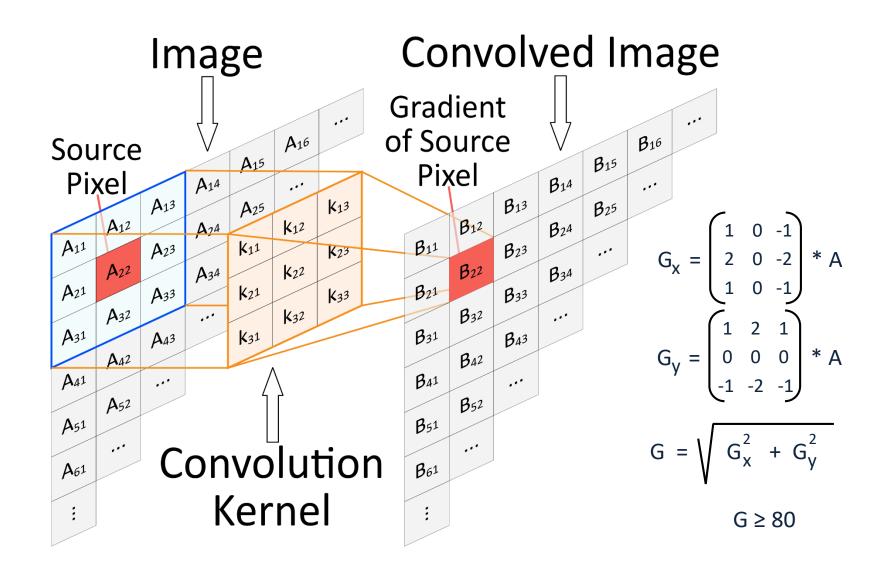

Test Case: Sobel and Prewitt edge detectors

Test Case: Sobel and Prewitt edge detectors

Test Case: Sobel and Prewitt edge detectors

| FPGA*             |                | MDC+CAPH |       | Н        | MDC+XRO |        | NOS XRONOS |        | vs CAPH |

|-------------------|----------------|----------|-------|----------|---------|--------|------------|--------|---------|

|                   |                | Altera   | Xil   | inx      | Altera  | >      | Kilinx     | Altera | Xilinx  |

| REG               |                | 1484     | 780   |          | -       |        | 632        | -      | -18,97% |

| LOGIC             |                | 1047     | 2347  |          | -       | 1533   |            | -      | -34,68% |

| RAM               |                | 15       | 0     |          | -       |        | 6.5        | -      | +100%   |

| DSP               |                | 36       | 36    |          | -       | 0      |            | -      | -100%   |

| MAX FREQ<br>[MHz] |                | 105,80   | 93,69 |          | -       | 142,86 |            | -      | +58,50% |

| EXEC TIME         | [cck]          | 15340    | 15340 |          | -       | 15348  |            | -      | +0,05%  |

|                   | ASIC**         |          |       | MDC+CAPH |         |        | MDC+XRONOS |        |         |

|                   | AREA [kGE]     |          |       | 466,90   |         |        |            | -      |         |

|                   | Max Freq [MHz] |          |       | 399.04   |         |        |            | -      |         |

\*target: Xilinx XXX Zynq-7 FPGA \*\*target: TMSC 45 nm CMOS technology

Test Case: Sobel and Prewitt edge detectors

| entity thr is<br>port (<br>i_empty: in std_logic;<br>i: in std_logic vector(13 downto 0);<br>CAPH VHDL | module thr_0(o_SEND, i_DATA, i_ACK,<br>o_RDY, i_COUNT, o_ACK, CLK, RESET,<br>i_SEND, o_COUNT, o_DATA);<br>wire thrSof go; |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| i_rd: <b>out</b> std_logic;                                                                            | output o_SEND;                                                                                                            |  |  |  |  |  |

| o_full: <b>in</b> std_logic;                                                                           | input [13:0] i_DATA;                                                                                                      |  |  |  |  |  |

| o: out std_logic_vector(9 downto 0);                                                                   | output i_ACK;                                                                                                             |  |  |  |  |  |

| o_wr: <b>out</b> std_logic;                                                                            | wire thr_done;                                                                                                            |  |  |  |  |  |

| clock: in std_logic;                                                                                   | wire thrSof_done;                                                                                                         |  |  |  |  |  |

| reset: in std_logic                                                                                    | input o_RDY;                                                                                                              |  |  |  |  |  |

| );                                                                                                     | input [15:0] i_COUNT;                                                                                                     |  |  |  |  |  |

| end thr;                                                                                               | ····                                                                                                                      |  |  |  |  |  |

| architecture FSM of thr is                                                                             | assign thrSof_go=scheduler_u214;<br>assign o SEND=or 024e0490 u0;                                                         |  |  |  |  |  |

| <b>begin</b><br>comb: <b>process</b> (i, i empty, o full)                                              | assign 0_SEND=01_024e0490_00;<br>assign i_ACK=or_173c13d7_u0;                                                             |  |  |  |  |  |

| variable p_p : signed(13 downto 0);                                                                    | assign thr_done=bus_50b9a749_;                                                                                            |  |  |  |  |  |

| begin                                                                                                  |                                                                                                                           |  |  |  |  |  |

| i.rdy, i=4096, o.rdy / rd(i), wr(o,256)                                                                | thr 0 scheduler                                                                                                           |  |  |  |  |  |

| if i_empty='0' and from_std_logic_vector(i,14)=to_signed(4096,14) and o_full='0'                       | thr 0 scheduler instance(.CLK(CLK),                                                                                       |  |  |  |  |  |

| then                                                                                                   | .RESET(bus_3fb49b2f_), .GO(bus_72d0efa6_),                                                                                |  |  |  |  |  |

| i rd <= '1';                                                                                           | .port_431807df_(o_RDY),                                                                                                   |  |  |  |  |  |

| o <= std_logic_vector(to_unsigned(256,10));                                                            | .port_74145b7a_(i_DATA),                                                                                                  |  |  |  |  |  |

| o_wr <= '1';                                                                                           | .port_64e9829f_(thrEoF_done),                                                                                             |  |  |  |  |  |

| i.rdy, i=8192, o.rdy / rd(i), wr(o,512)                                                                | .port_3adf3763_(thr_done),                                                                                                |  |  |  |  |  |

| elsif i_empty='0' and from_std_logic_vector(i,14)=to_signed(8192,14) and o_full='0'                    | .port_1779a109_(i_SEND),                                                                                                  |  |  |  |  |  |

| then                                                                                                   | .port_0bb7799c_(thrSof_done),                                                                                             |  |  |  |  |  |

|                                                                                                        | .DONE(thr_0_scheduler_instance_DONE),                                                                                     |  |  |  |  |  |

| end if;                                                                                                | .RESULT(scheduler),                                                                                                       |  |  |  |  |  |

| end process;                                                                                           | .RESULT_u981(scheduler_u214),                                                                                             |  |  |  |  |  |

| seq: <b>process</b> (clock, reset)                                                                     | .RESULT_u982(scheduler_u215));                                                                                            |  |  |  |  |  |

| begin                                                                                                  | thr_0_thrSof                                                                                                              |  |  |  |  |  |

| if (reset='0') then                                                                                    | thr_O_thrSof_instance(.CLK(CLK),                                                                                          |  |  |  |  |  |

| elsif rising_edge(clock) then<br>end if;                                                               | .GO(thrSof_go), .port_269cbf08_(i_DATA),<br>.DONE(thr_0_thrSof_instance_DONE),                                            |  |  |  |  |  |

| end n,<br>end process;                                                                                 | .RESULT(thrSof), .RESULT u983(thrSof u3),                                                                                 |  |  |  |  |  |

| end FSM;                                                                                               | .RESULT_u984(thrSof_u4),                                                                                                  |  |  |  |  |  |

|                                                                                                        | .RESULT_u985(thrSof_u5));                                                                                                 |  |  |  |  |  |

|                                                                                                        | endmodule                                                                                                                 |  |  |  |  |  |

# Outline

- Introduction

- Embedded Moving Toward IoT and CPS

- Computing Architectures for Embedded Systems

- Background

- CGRA Design From Applications to Architecture

- CGRA Design Open Issues

- CGRA Composition and Management

- High Level Synthesis

- Results

- Functional vs. Imperative HLS for CGRA

- Target Specific vs. Independent HLS for CGRA

- Final Remarks

# **Final Remarks**

- Modern **embedded systems**, pushed into the IoT and CPS era, have **lots of colliding requirements**.

- **Coarse-Grained Reconfigurable Architectures** (CGRAs) could be a **suitable solution** to meet these requirements.

- The development of CGRAs require **HLS support** to complete **design automation**

- Functional HLS outperforms imperative HLS for this specific kind of architectures

- Target specific HLS is more efficient on its target, but it lacks in code compactness and readability

# Thanks To ...

EU Commission for funding the **CERBERO** (*Cross-layer modEl-based fRamework for multi-oBjective dEsign of Reconfigurable systems in unceRtain hybRid envirOnments*) project as part of the H2020 Programme under grant agreement No 732105.

#### **Coordinator:**

Michal Masin (IBM), michaelm@il.ibm.com

#### **Scientific Coordinator:**

Francesca Palumbo (UniSS), fpalumbo@uniss.it

#### **Innovation Manager:**

Katiuscia Zedda (Abinsula), katiuscia.zedda@abinsula.com

#### **Dissemination-Communication Manager:**

Francesco Regazzoni (USI), francesco.regazzoni@usi.ch

#### Platform-Agnostic Dataflow-to-Hardware Design Flow for Reconfigurable Systems

Francesca Palumbo, Claudio Rubattu, Carlo Sau, Luigi Raffo and Maxime Pelcat

Alghero (Italy) – September 25-30, 2017

Designing Cyber-Physical Systems – From concepts to implementation Distinguished lecturers: Alberto Sangiovanni-Vincentelli, XXX Application deadline: July XXth, 2018 http://www.cpsschool.eu/

#### Naples, 20-22 June 2018