Centro de Electrónica Industrial - UPM 30 May 2018

#### Multi-Grain Reconfiguration for Advanced Adaptivity in Cyber-Physical Systems

#### Tiziana Fanni – *tiziana.fanni@diee.unica.it* Università degli Studi di Cagliari

Horizon 2020 European Union funding for Research & Innovation

# Reconfigurable systems design and development of code generation tools for low power reconfigurable hardware architectures.

#### **UNIVERSITY OF SASSARI**

#### **UNIVERSITY OF CAGLIARI**

# Outline

- Concepts & Definition

- Self-Adaptation in Cyber-Physical Systems

- Types of Adaptation

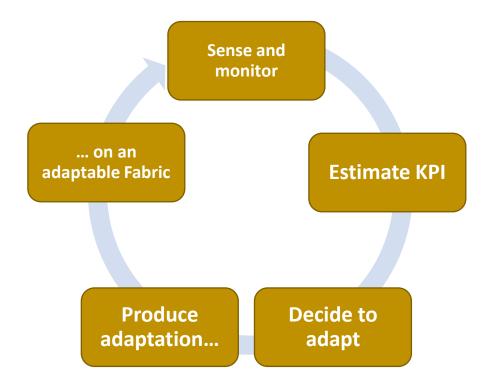

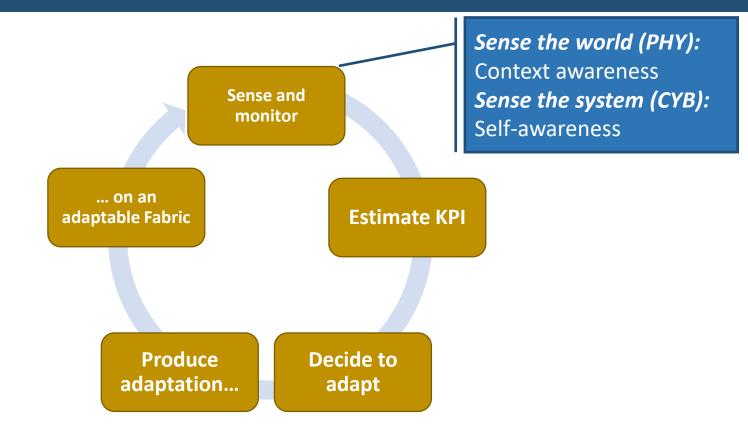

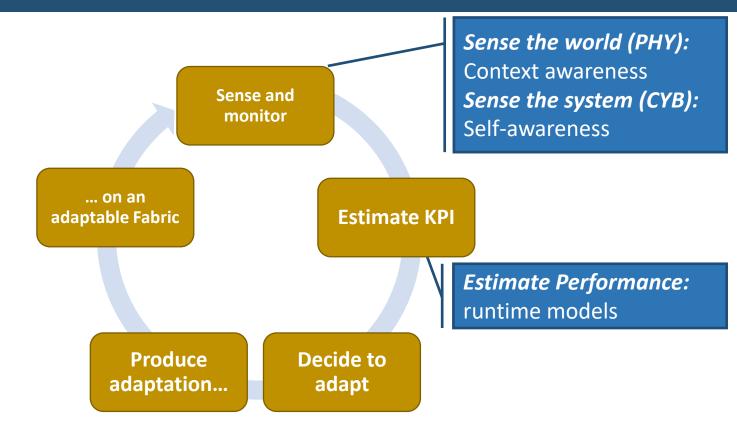

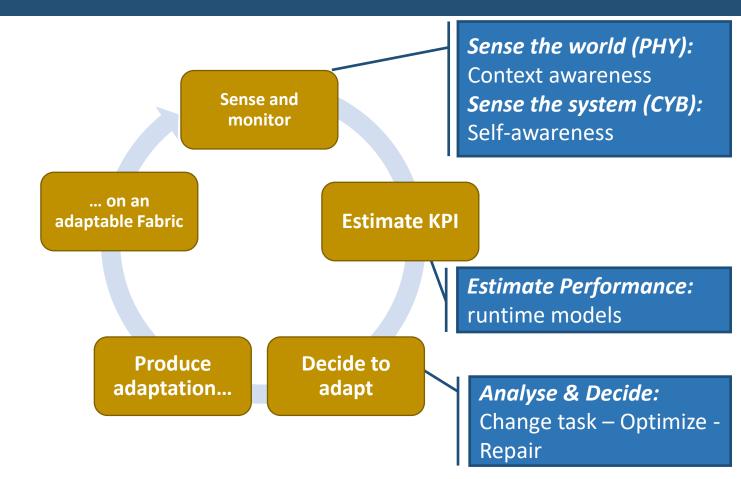

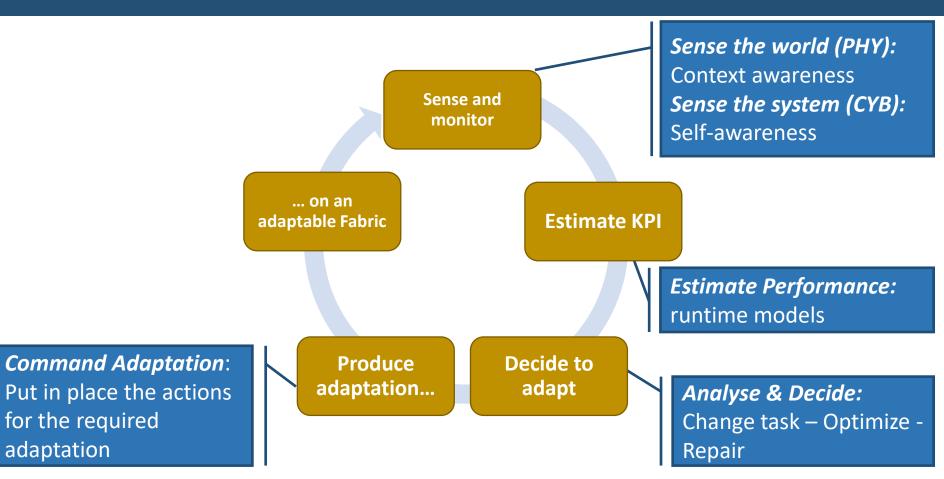

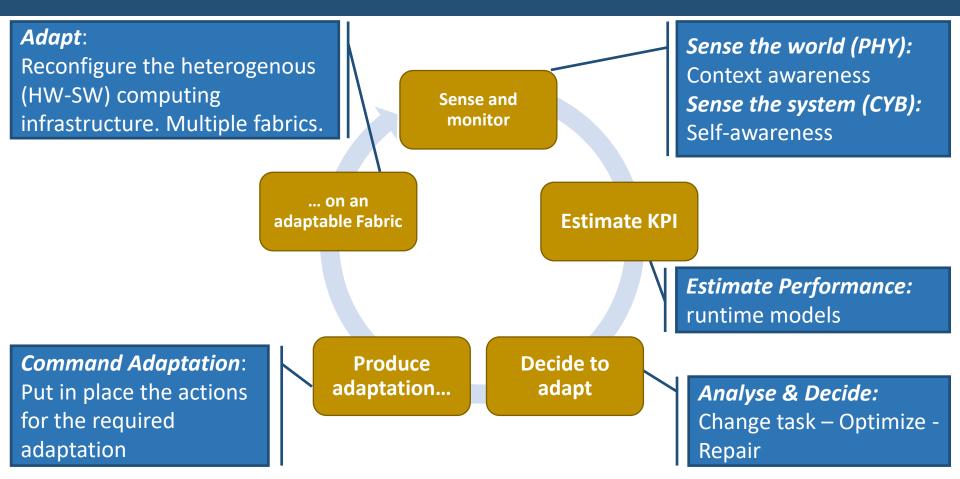

- The Adaptation Loop

- Adaptive CPS: The CERBERO approach

- Self-Adaptation in CERBERO H2020

- Adaptation Fabrics in CERBERO H2020

- HW Adaptation in CERBERO

- ARTICo3

- MDC-compliant CG adaptation

- Mixed-Grain Adaptivity

- ARTICo3 + MDC integration

- Next-steps

- Monitoring

- Adaptivity Support

# Outline

- Concepts & Definition

- Self-Adaptation in Cyber-Physical Systems

- Types of Adaptation

- The Adaptation Loop

- Adaptive CPS: The CERBERO approach

- Self-Adaptation in CERBERO H2020

- Adaptation Fabrics in CERBERO H2020

- HW Adaptation in CERBERO

- ARTICo3

- MDC-compliant CG adaptation

- Mixed-Grain Adaptivity

- ARTICo3 + MDC integration

- Next-steps

- Monitoring

- Adaptivity Support

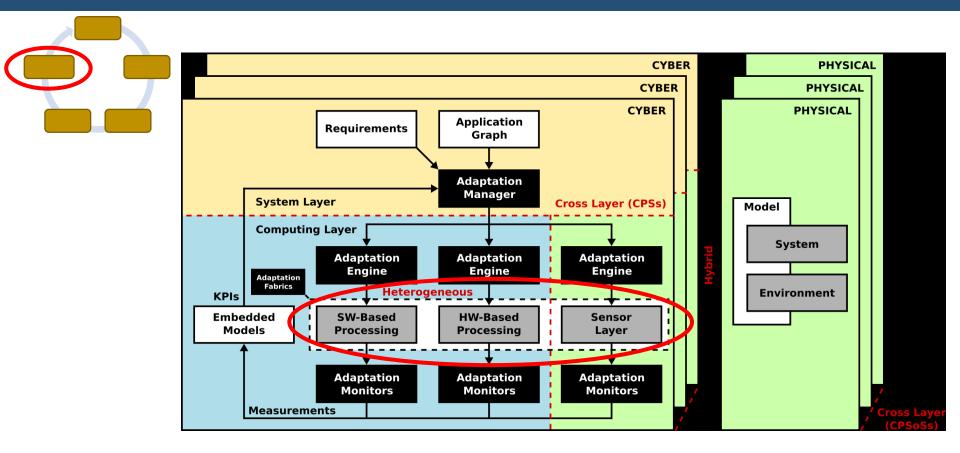

**ENVIRONMENTAL AWARENESS**: Influence of the environment on the system, i.e. daylight vs. nocturnal, radiation level changes, etc. Sensors are needed to interact with the environment and capture conditions

variations.

**ENVIRONMENTAL AWARENESS**: Influence of the environment on the system, i.e. daylight vs. nocturnal, radiation level changes, etc. Sensors are needed to interact with the environment and capture conditions variations.

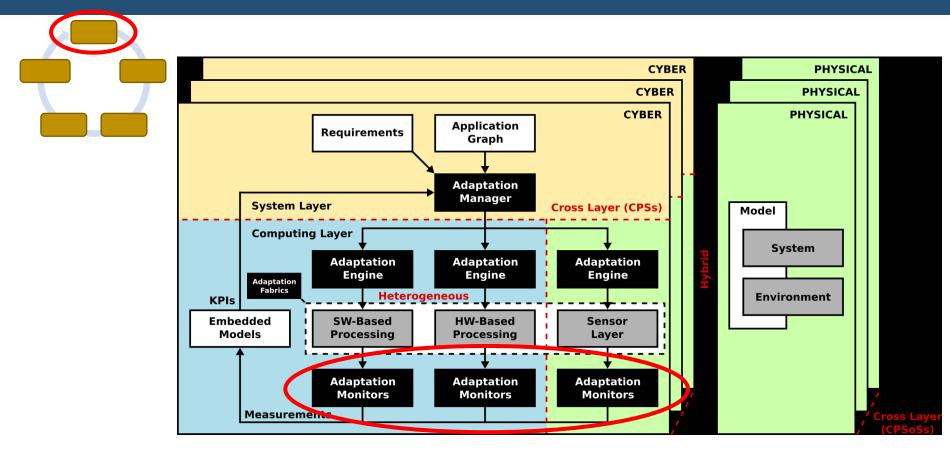

**USER-COMMANDED**: System-User interaction, i.e. user preferences, etc. Proper human-machine interfaces are needed to enable interaction and capture commands.

**ENVIRONMENTAL AWARENESS**: Influence of the environment on the system, i.e. daylight vs. nocturnal, radiation level changes, etc. Sensors are needed to interact with the environment and capture conditions variations.

**USER-COMMANDED**: System-User interaction, i.e. user preferences, etc. Proper human-machine interfaces are needed to enable interaction and capture commands.

**SELF-AWARENESS**: The internal status of the system varies while operating and may lead to reconfiguration needs, i.e. chip temperature variation, low battery. Status monitors are needed to capture the status of the system.

# Outline

- Concepts & Definition

- Self-Adaptation in Cyber-Physical Systems

- Types of Adaptation

- The Adaptation Loop

- Adaptive CPS: The CERBERO approach

- Self-Adaptation in CERBERO H2020

- Adaptation Fabrics in CERBERO H2020

- HW Adaptation in CERBERO

- ARTICo3

- MDC-compliant CG adaptation

- Mixed-Grain Adaptivity

- ARTICo3 + MDC integration

- Next-steps

- Monitoring

- Adaptivity Support

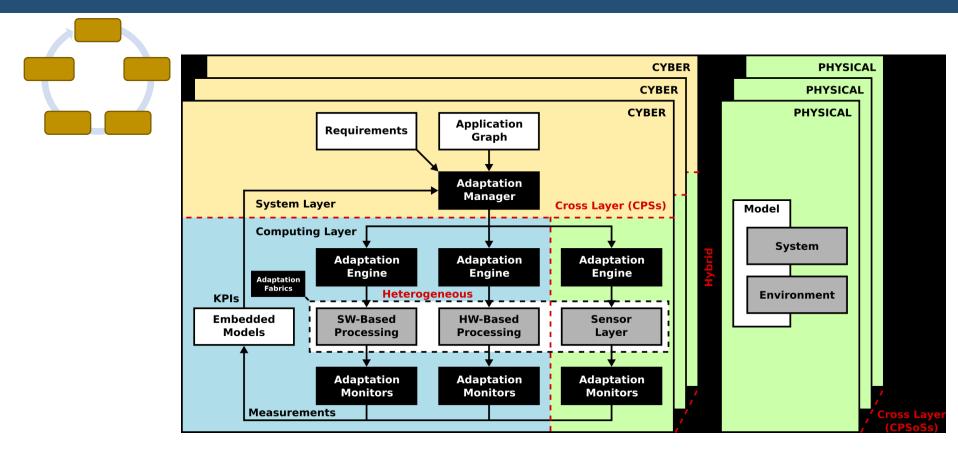

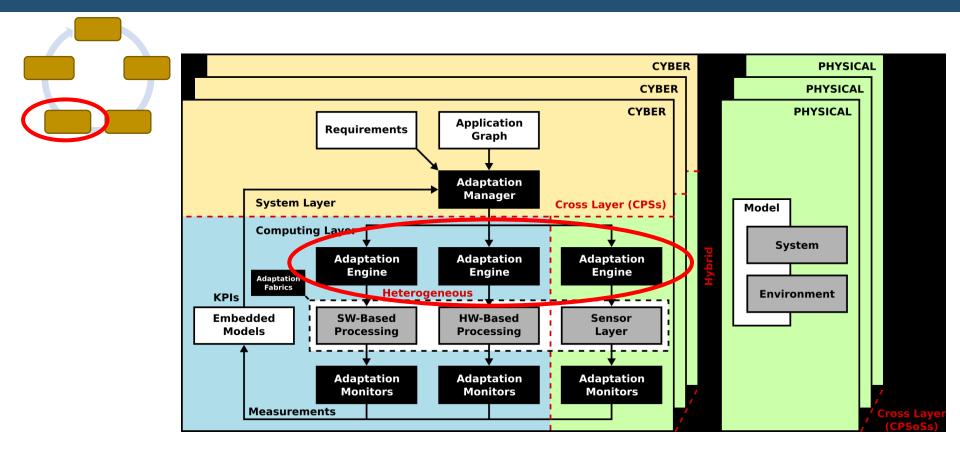

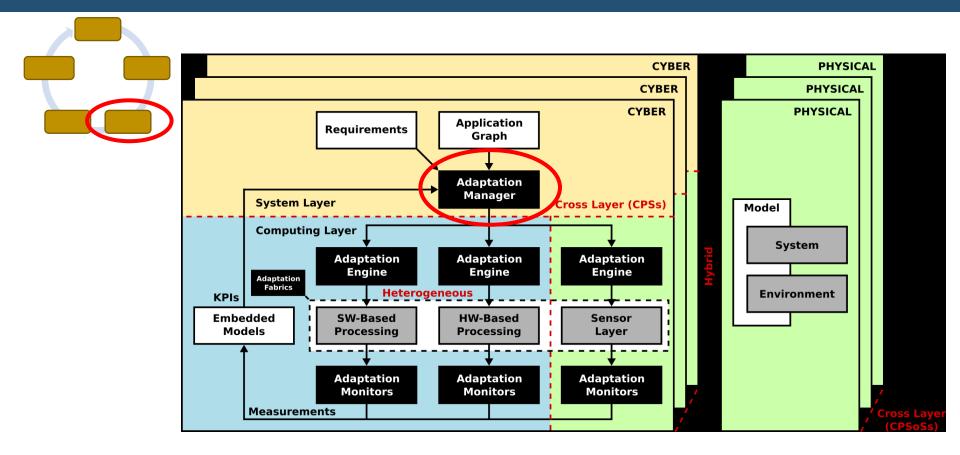

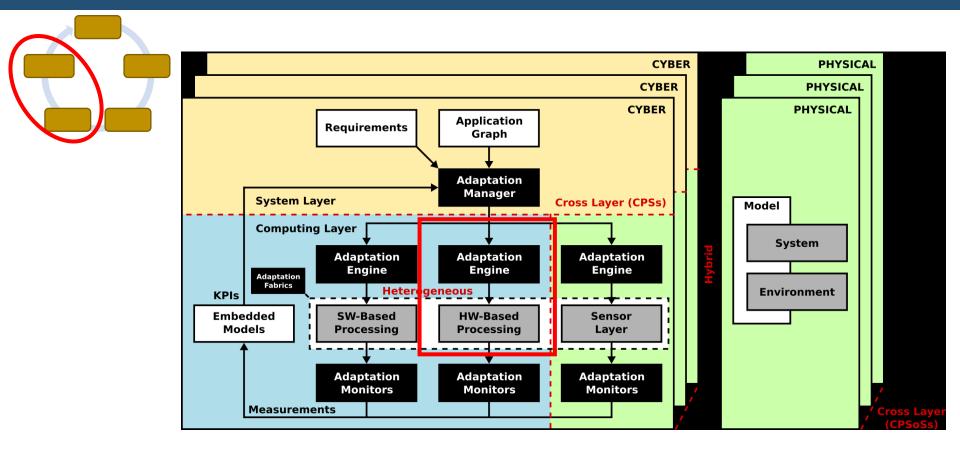

### **Adaptation fabrics in CERBERO H2020**

# Outline

- Concepts & Definition

- Self-Adaptation in Cyber-Physical Systems

- Types of Adaptation

- The Adaptation Loop

- Adaptive CPS: The CERBERO approach

- Self-Adaptation in CERBERO H2020

- Adaptation Fabrics in CERBERO H2020

- HW Adaptation in CERBERO

- ARTICo3

- MDC-compliant CG adaptation

- Mixed-Grain Adaptivity

- ARTICo3 + MDC integration

- Next-steps

- Monitoring

- Adaptivity Support

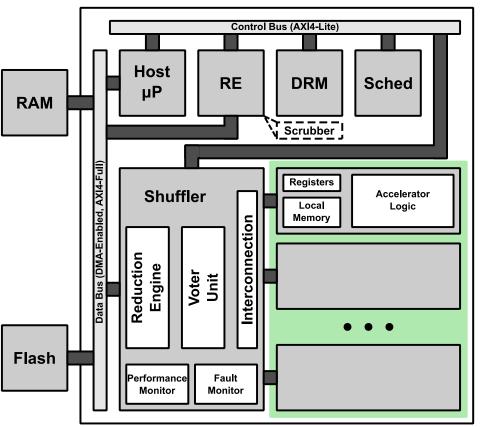

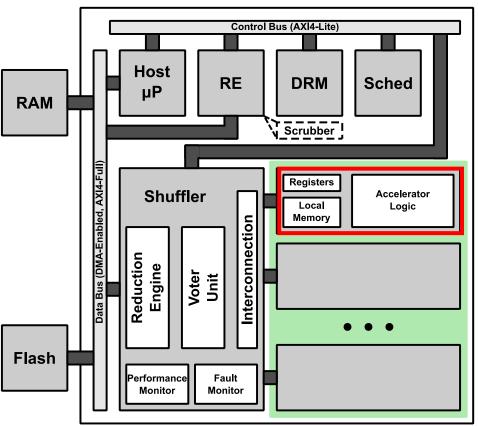

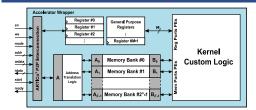

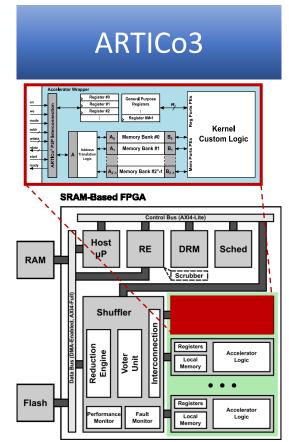

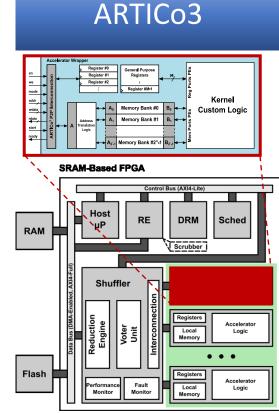

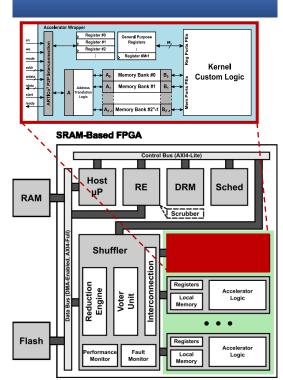

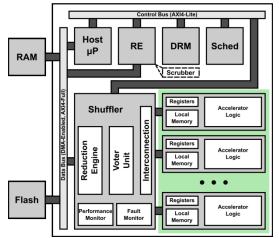

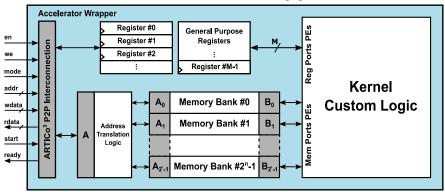

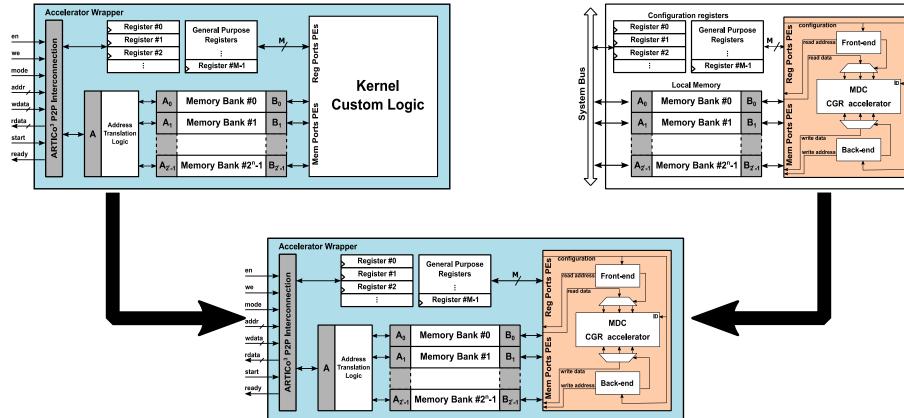

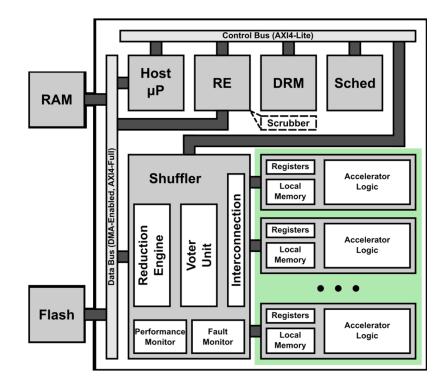

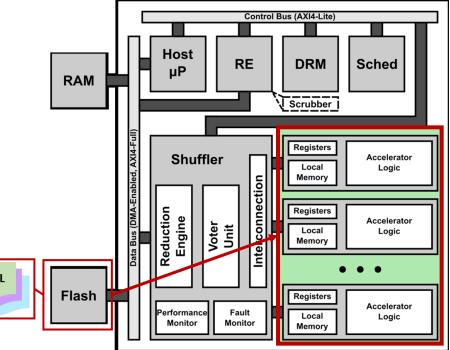

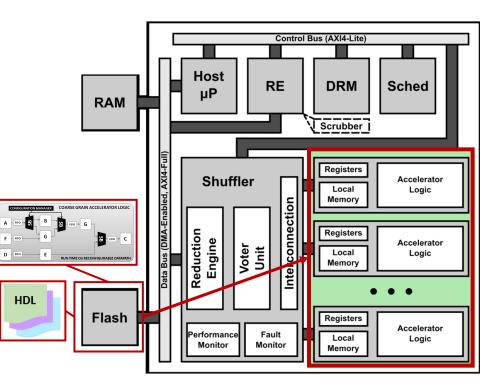

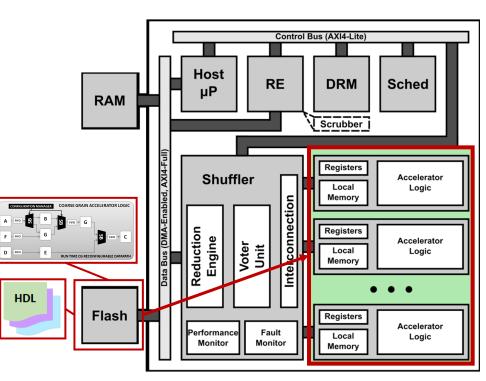

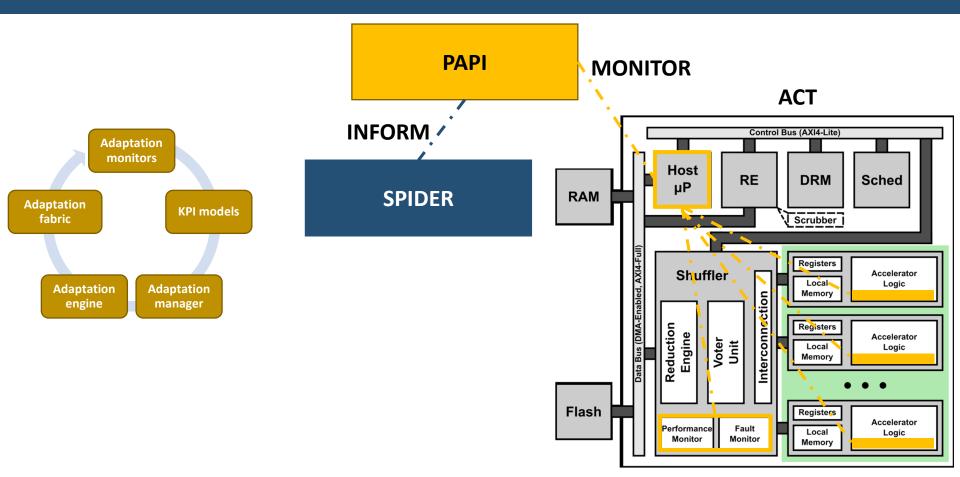

# **ARTICo<sup>3</sup>** Architecture

#### Control Bus (AXI4-Lite) Host RE DRM Sched μP RAM Scrubber Data Bus (DMA-Enabled, AXI4-Full) Registers Shuffler Accelerator Local Logic Memory Interconnection Registers Reduction Engine Accelerator Voter Unit Local Logic Memory Flash Performance Fault Monitor Monitor

#### SRAM-Based FPGA

- Multiple accelerators providing performance scalability and adaptive fault tolerance

- Coalesced transactions for fast data exchange via AXI4-full

- Runtime support by ARTICo<sup>3</sup> API

- It follows a data-parallel MoC, similar to GPUs

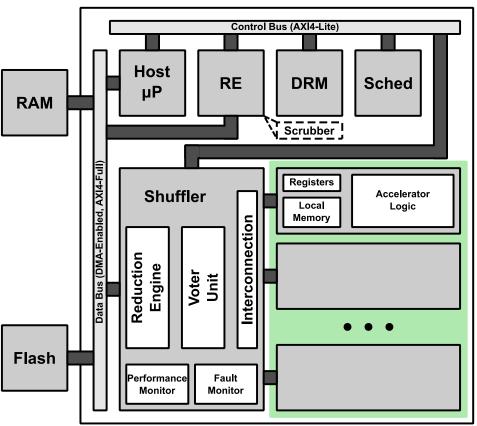

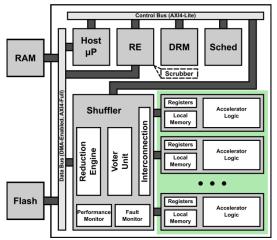

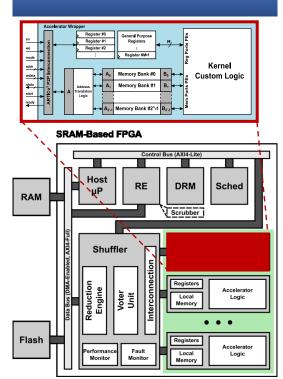

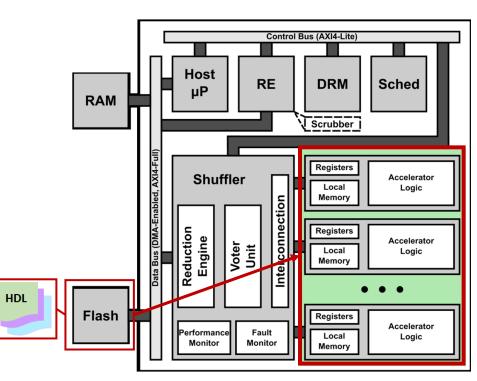

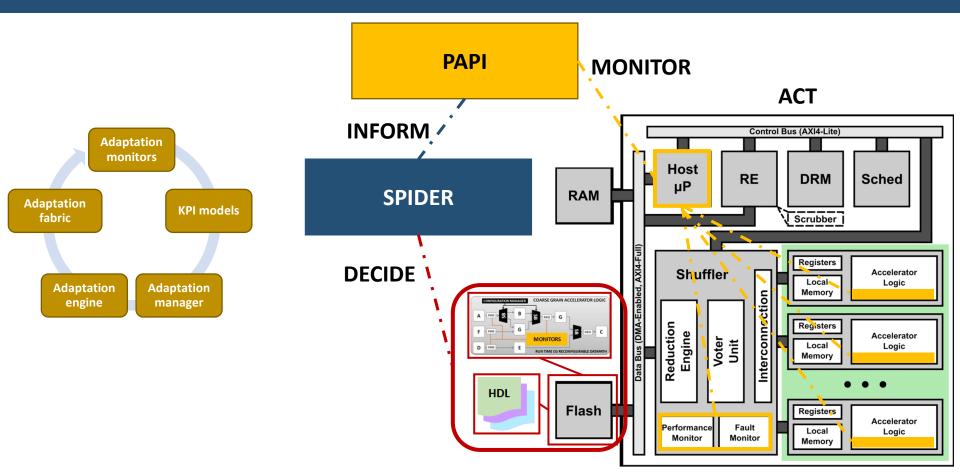

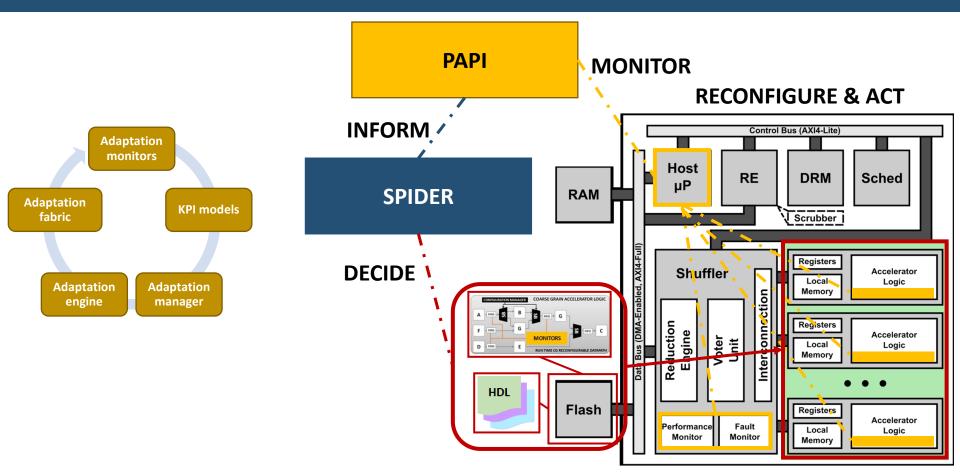

# **ARTICo<sup>3</sup>** Architecture

#### Control Bus (AXI4-Lite) Host RE DRM Sched μP RAM Scrubber Data Bus (DMA-Enabled, AXI4-Full) Registers Shuffler Accelerator Local Logic Memory Interconnection Registers Reduction Engine Accelerator Voter Unit Local Logic Memory Flash Registers Accelerator Performance Fault Local Logic Monitor Monitor Memory

#### SRAM-Based FPGA

- Multiple accelerators providing performance scalability and adaptive fault tolerance

- Coalesced transactions for fast data exchange via AXI4-full

- Runtime support by ARTICo<sup>3</sup> API

- It follows a data-parallel MoC, similar to GPUs

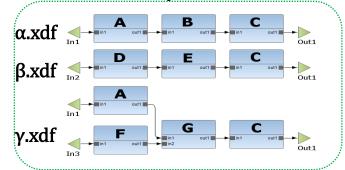

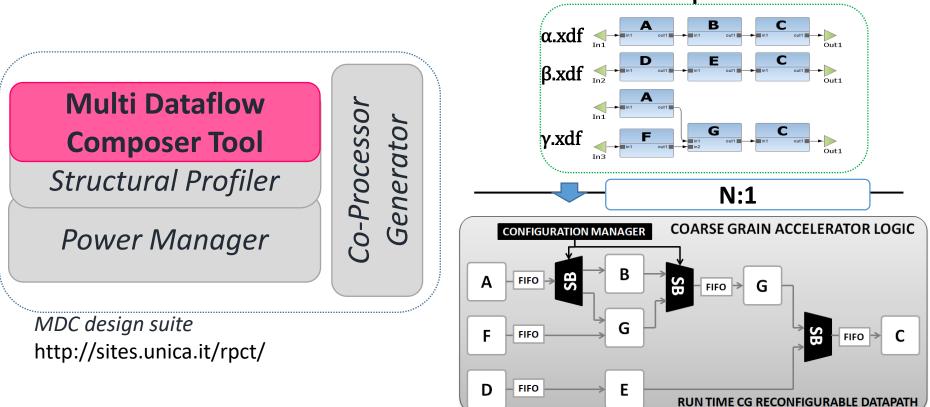

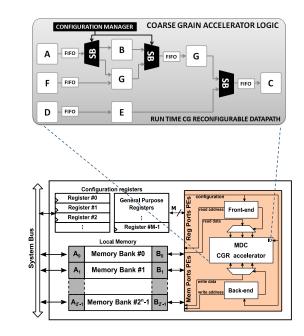

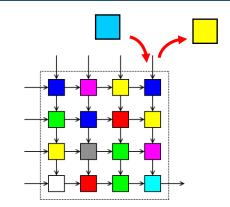

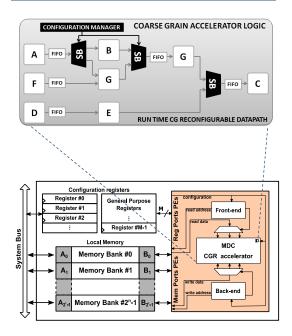

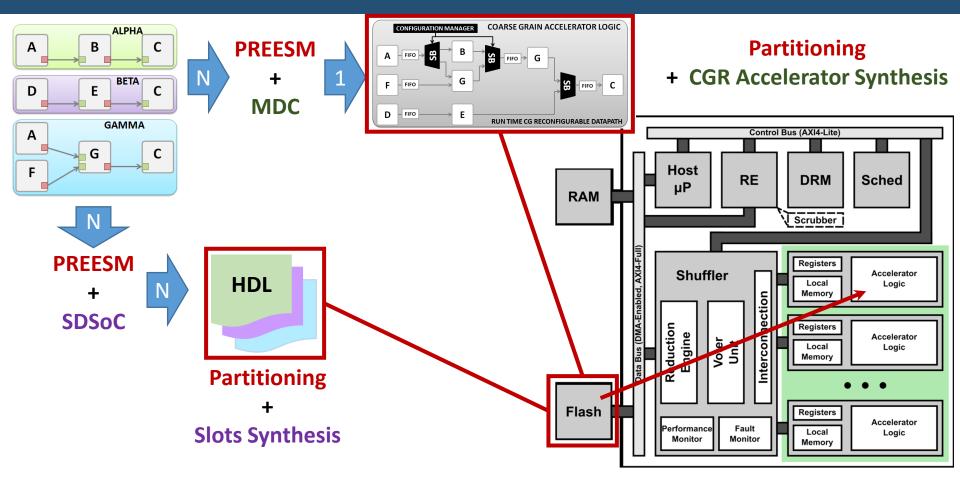

# MDC tool: Dataflow to HW Mapping

MDC design suite http://sites.unica.it/rpct/

# **MDC tool: Dataflow to HW Mapping**

**Dataflow Specifications**

MDC design suite http://sites.unica.it/rpct/

# **MDC tool: Dataflow to HW Mapping**

**Dataflow Specifications**

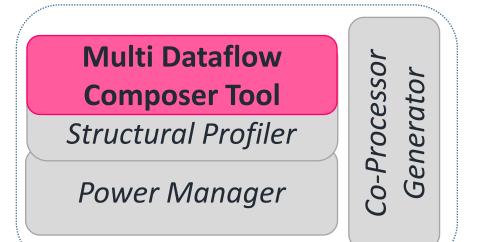

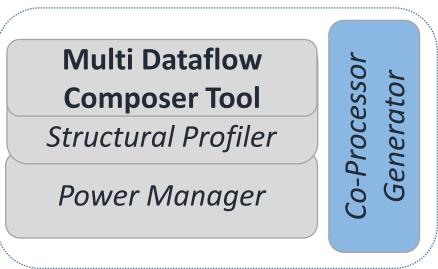

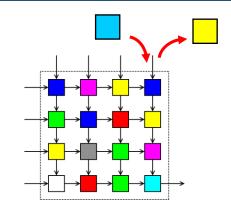

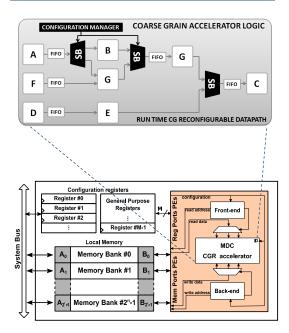

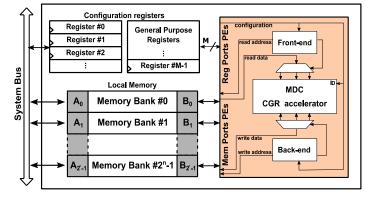

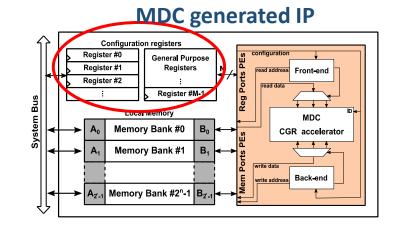

# **MDC Tool: Coprocessor Generator**

MDC design suite http://sites.unica.it/rpct/

#### **Co-Processor Generator**:

generation of ready-to-use Xilinx IPs

# **MDC Tool: Coprocessor Generator**

MDC design suite http://sites.unica.it/rpct/

#### **Co-Processor Generator:**

#### generation of ready-to-use Xilinx IPs

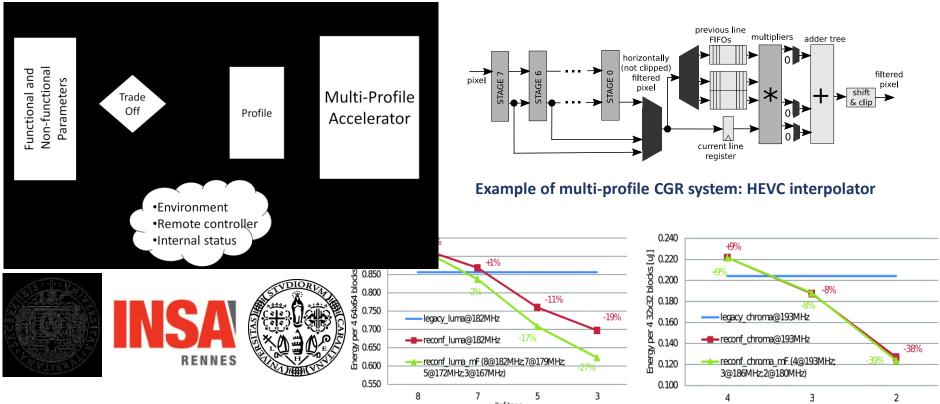

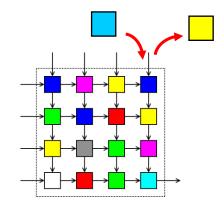

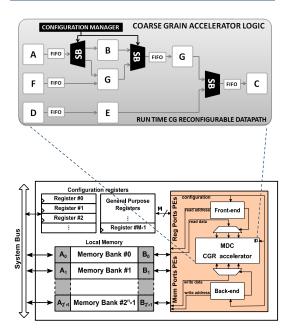

#### **CG Reconfiguration: Runtime KPI Trade-Offs**

[ESL17] Carlo Sau, Francesca Palumbo, Maxime Pelcat, Julien Heulot, Erwan Nogues, Daniel Menard, Paolo Meloni, and Luigi Raffo. "*Challenging the*"Between Fixed FPGA Interpolators with Reconfigurable and Multi-frequency Approximate Computing" in IEEE Embedded Systems Letters, vol. 9, no. 3, pp. 65-68, Sept. 2017.

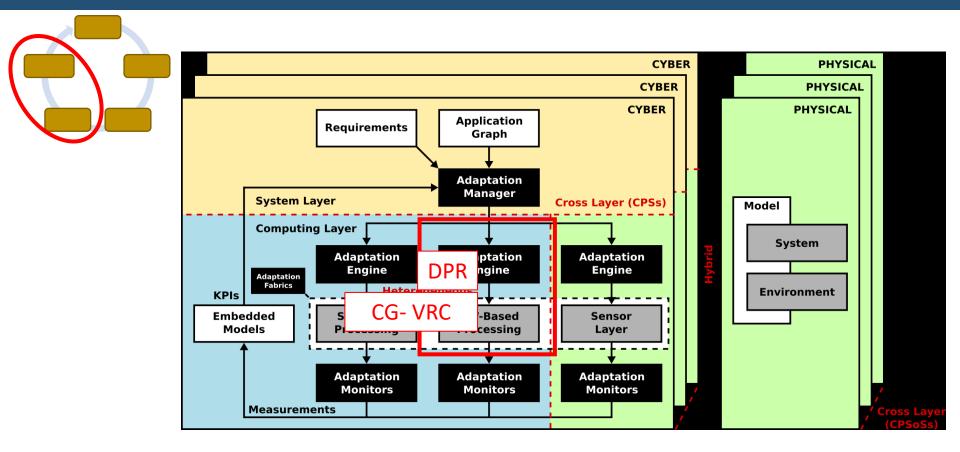

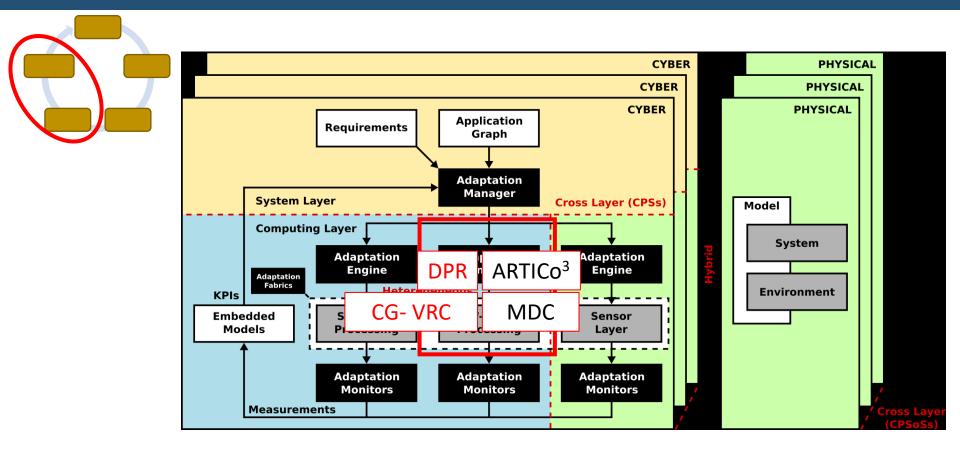

#### **DPR** $\rightarrow$ Dynamic and Partial Reconfiguration

- Lower reconfiguration speeds

- Better operation speed (no mux/less logic)

- Better Resource Utilization (no dark logic)

- Higher Flexibility and Scalability

- Technology dependent (FPGA)

#### **DPR** $\rightarrow$ Dynamic and Partial Reconfiguration

- Lower reconfiguration speeds

- Better operation speed (no mux/less logic)

- Better Resource Utilization (no dark logic)

- Higher Flexibility and Scalability

- Technology dependent (FPGA)

#### **DPR** $\rightarrow$ Dynamic and Partial Reconfiguration

- Lower reconfiguration speeds

- Better operation speed (no mux/less logic)

- Better Resource Utilization (no dark logic)

- Higher Flexibility and Scalability

- Technology dependent (FPGA)

**CG-VRC** → Coarse Grain - Virtual Reconfigurable Circuits

#### **DPR** $\rightarrow$ Dynamic and Partial Reconfiguration

- Lower reconfiguration speeds

- Better operation speed (no mux/less logic)

- Better Resource Utilization (no dark logic)

- Higher Flexibility and Scalability

- Technology dependent (FPGA)

#### **CG-VRC** → Coarse Grain - Virtual Reconfigurable Circuits

- High reconfiguration speed

- Lower operation speed (mux and size)

- Higher Area Overhead

- Technology independent (ASIC or FPGA)

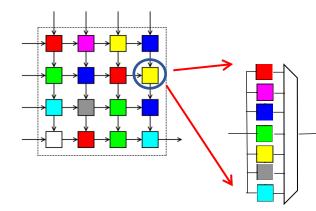

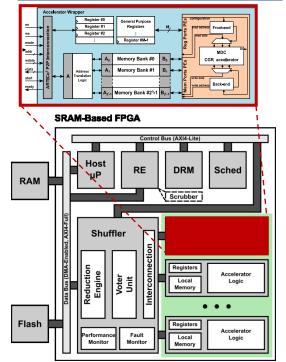

#### ARTICo3

#### SRAM-Based FPGA

#### Coarse-Grain MDC Logic

#### ARTICo3

#### Coarse-Grain MDC Logic

#### Mixed-Grain A3+MDC

#### SRAM-Based FPGA

#### Coarse-Grain MDC Logic

#### Mixed-Grain A3+MDC

## Outline

- Concepts & Definition

- Self-Adaptation in Cyber-Physical Systems

- Types of Adaptation

- The Adaptation Loop

- Adaptive CPS: The CERBERO approach

- Self-Adaptation in CERBERO H2020

- Adaptation Fabrics in CERBERO H2020

- HW Adaptation in CERBERO

- ARTICo3

- MDC-compliant CG adaptation

- Mixed-Grain Adaptivity

- ARTICo3 + MDC integration

- Next-steps

- Monitoring

- Adaptivity Support

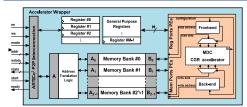

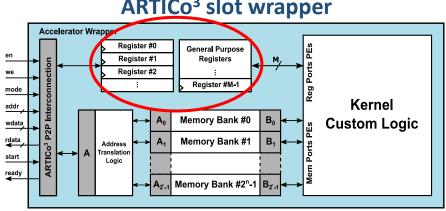

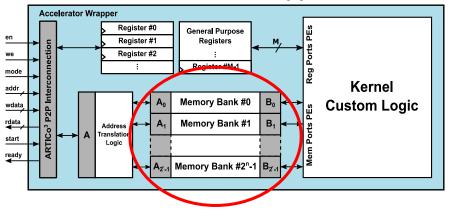

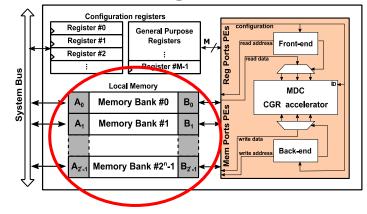

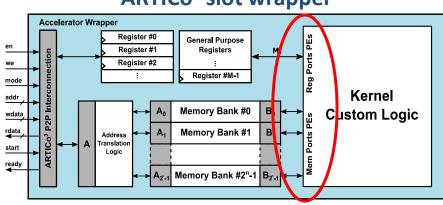

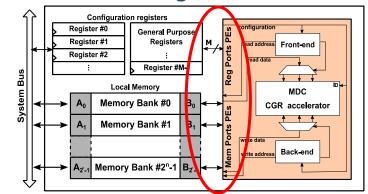

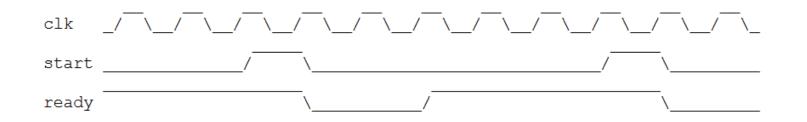

#### **ARTICo<sup>3</sup> slot wrapper**

#### **ARTICo<sup>3</sup> slot wrapper**

#### **ARTICo<sup>3</sup> slot wrapper**

#### **ARTICo<sup>3</sup> slot wrapper**

#### **ARTICo<sup>3</sup> slot wrapper**

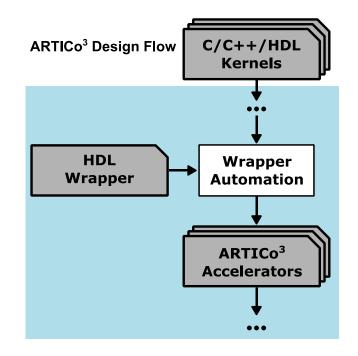

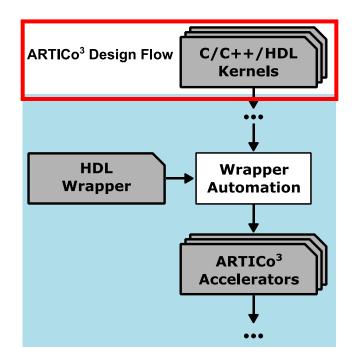

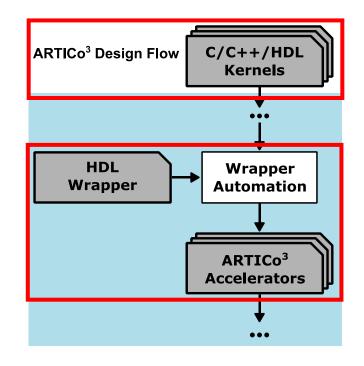

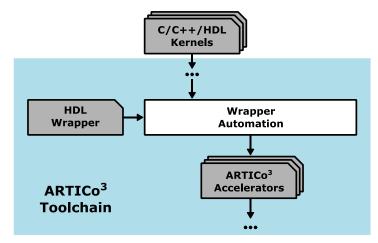

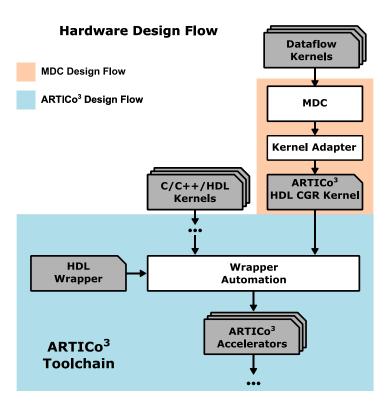

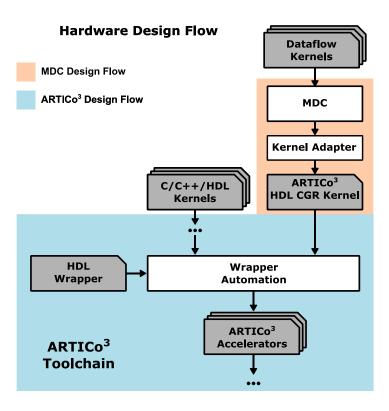

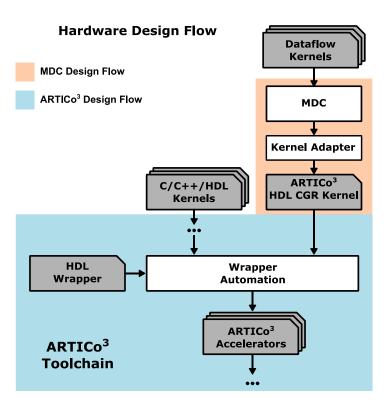

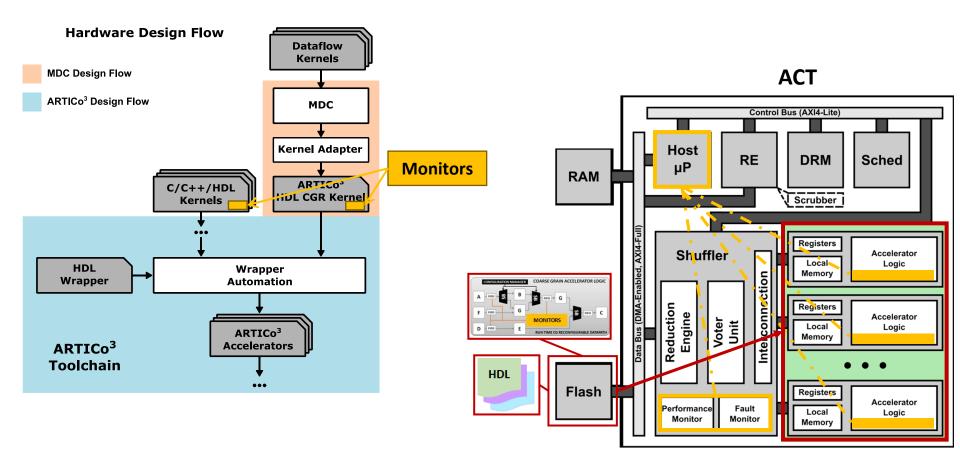

**Hardware Design Flow**

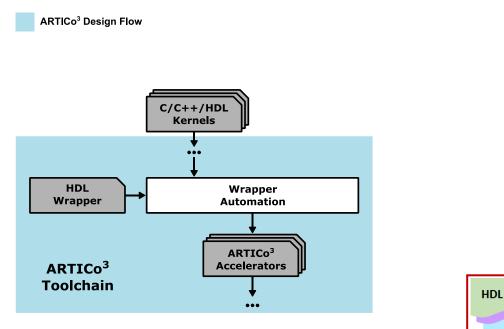

ARTICo<sup>3</sup> Design Flow

**Hardware Design Flow**

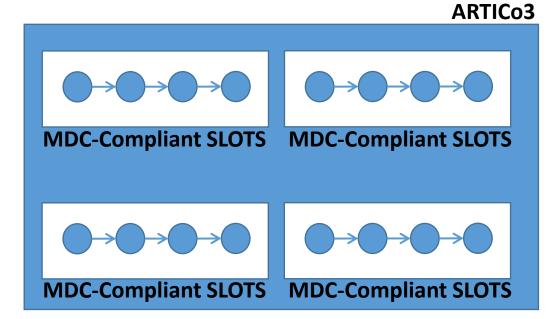

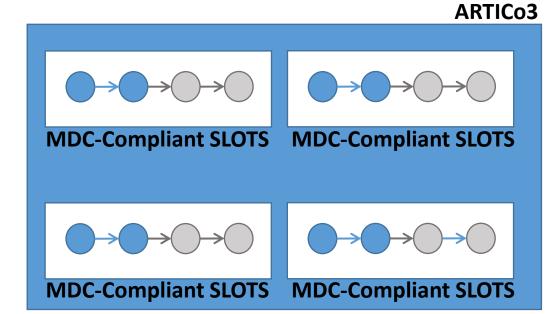

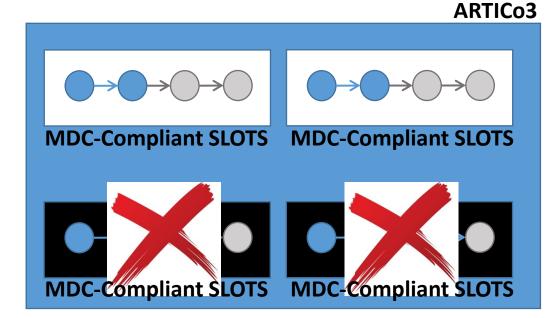

# ARTICo<sup>3</sup> + MDC: Mixed-Grain

Max Troughput Max QoS

# ARTICo<sup>3</sup> + MDC: Mixed-Grain

Max Troughput Max QoS

Max Troughput Degraded QoS

# ARTICo<sup>3</sup> + MDC: Mixed-Grain

Max Troughput Max QoS

Max Troughput Degraded QoS

Less Troughput Degraded QoS

# Outline

- Concepts & Definition

- Self-Adaptation in Cyber-Physical Systems

- Types of Adaptation

- The Adaptation Loop

- Adaptive CPS: The CERBERO approach

- Self-Adaptation in CERBERO H2020

- Adaptation Fabrics in CERBERO H2020

- HW Adaptation in CERBERO

- ARTICo3

- MDC-compliant CG adaptation

- Mixed-Grain Adaptivity

- ARTICo3 + MDC integration

- Next-steps

- Monitoring

- Adaptivity Support

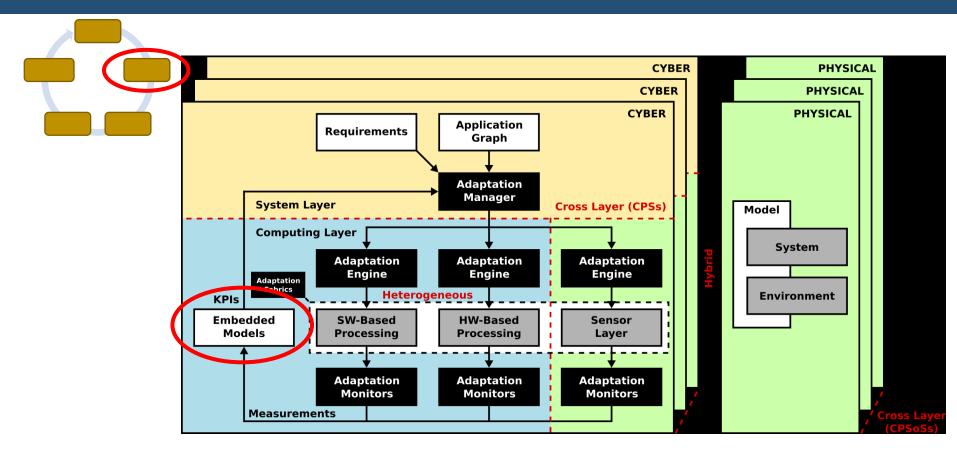

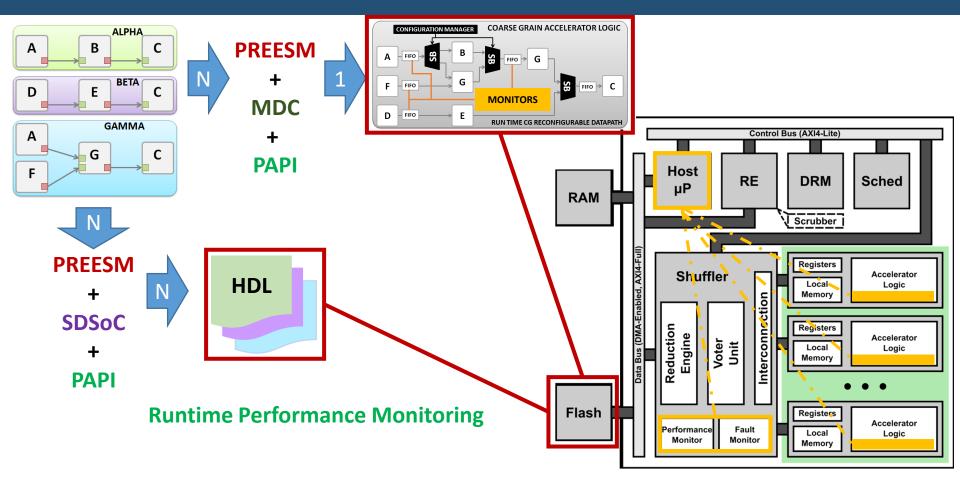

#### Self-Adaptation in CERBERO H2020: Monitors

### **Mixed-Grain Adaptivity**

#### **Mixed-Grain Self-Adaptivity**

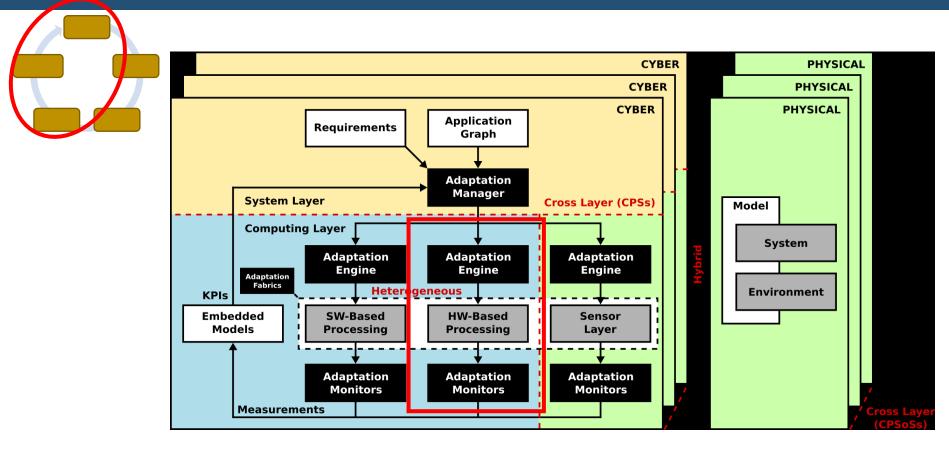

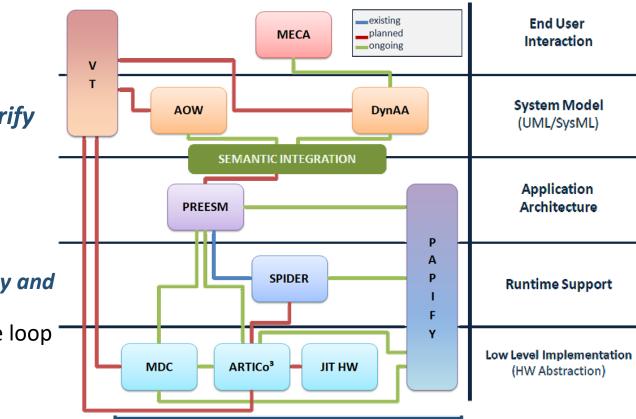

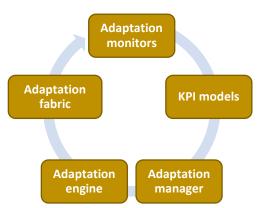

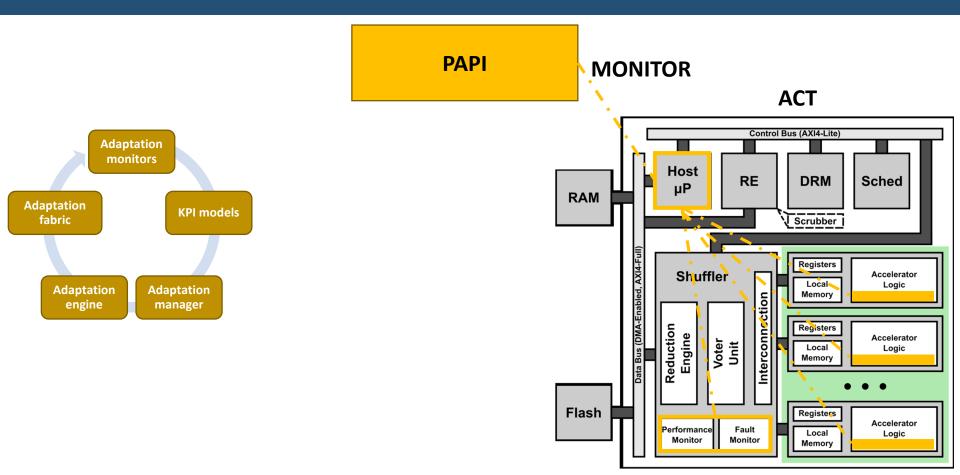

# Adaptivity Support: CERBERO Framework

- CERBERO Framework

- Integrated design environment to *model*, *explore, deploy and verify* complex *adaptive CPS*

- Address the lack of integrated toolchains capable of:

- Spanning across layers

- Dealing with adaptivity and heterogeneity

- Providing system in the loop co-simulation

# Adaptivity Support @ Design-Time

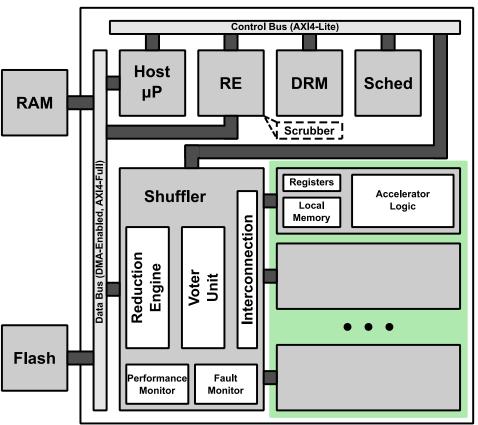

## Adaptivity Support @ Run-Time

Control Bus (AXI4-Lite) Host RE DRM Sched μP RAM Scrubber Data Bus (DMA-Enabled, AXI4-Full Registers Shuffler Accelerator Local Logic Memory Interconnection Reduction Engine Registers Accelerator Voter Unit Local Logic Memory • • Flash Registers Accelerator Performance Fault Local Logic Monitor Monitor Memory

ACT

Centro de Electrónica Industrial - UPM 30 May 2018

# Thank you for your attention

Tiziana Fanni – *tiziana.fanni@diee.unica.it* Università degli Studi di Cagliari

Horizon 2020 European Union funding for Research & Innovation