### Analysis of a Heterogeneous Multi-Core, Multi-HW-Accelerator-Based System Designed Using PREESM and SDSoC

Leonardo Suriano, Alfonso Rodriguez, Karol Desnos, Maxime Pelcat, Eduardo de la Torre

Universidad Politécnica de Madrid

## Introduction

#### Embedded World

...and many others

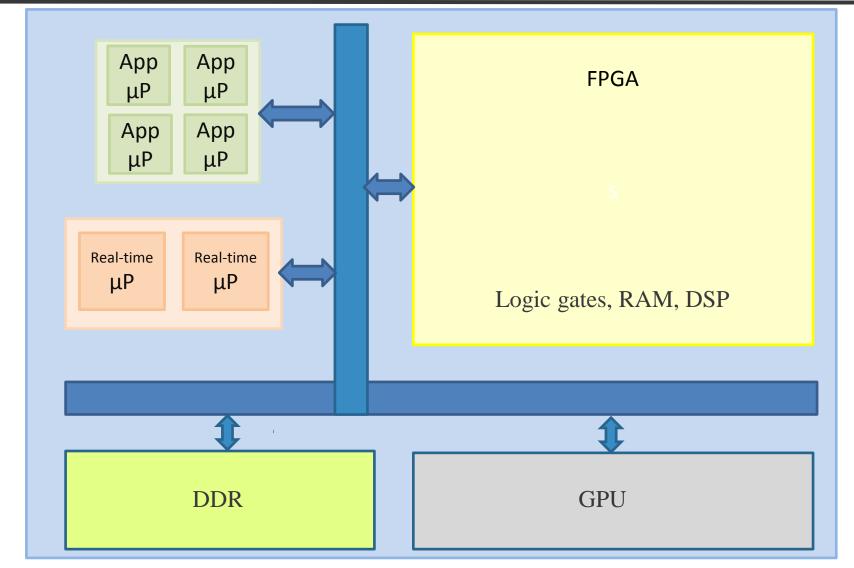

## **Heterogeneous devices**

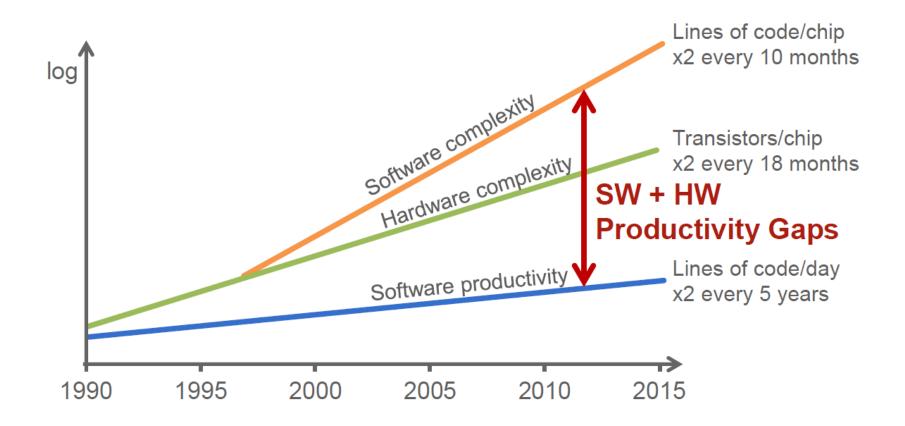

## SW + HW productivity GAP

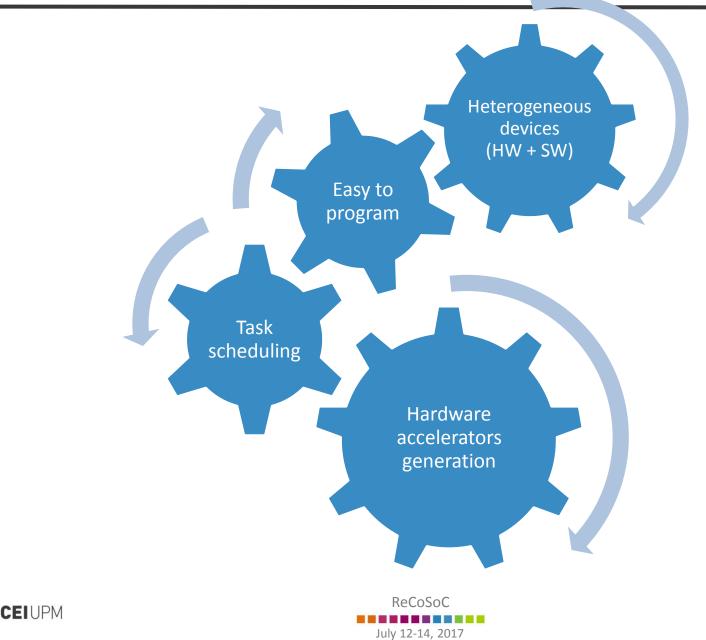

## GOAL

5

# **Main Contribution**

Rapid prototyping of software applications enabling:

- deadlock-free code generation using **PiSDF MoC**

- custom hardware acceleration and generation

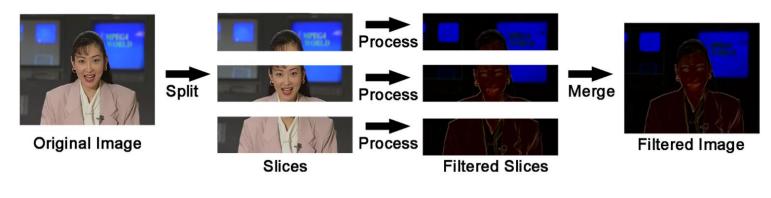

# **Video Processing Application**

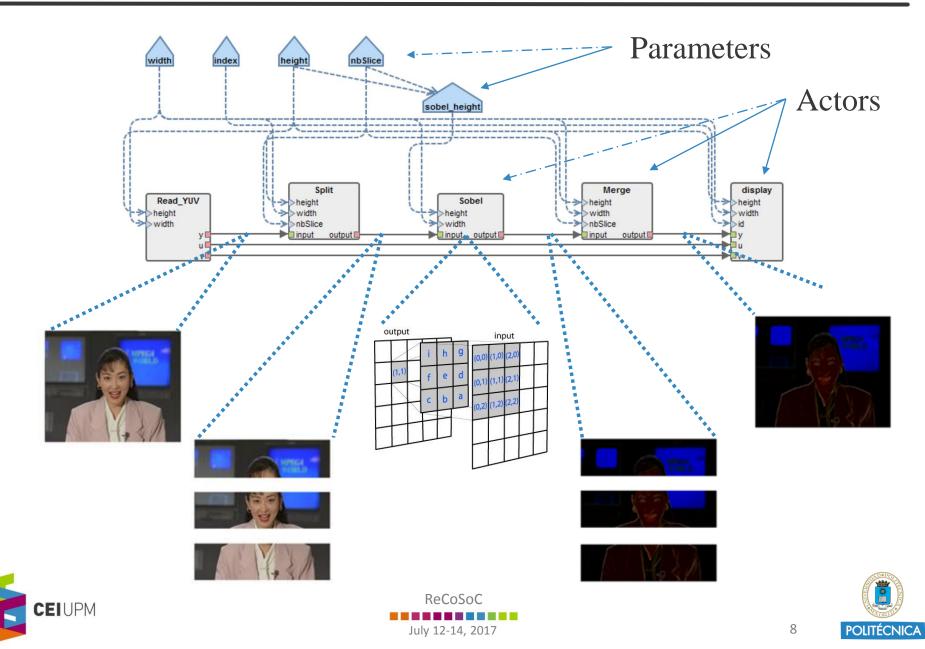

# **Actors Specification**

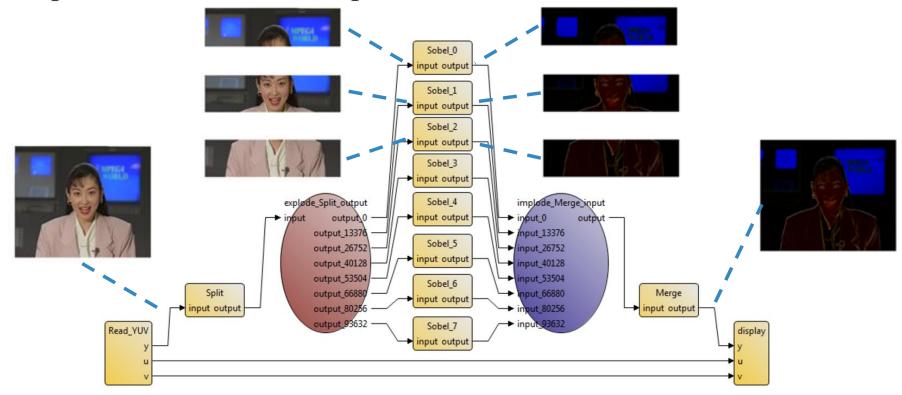

# **Exposed parallelism**

**Equivalent single-rate graph** where each edge has equal production and consumption rates of token.

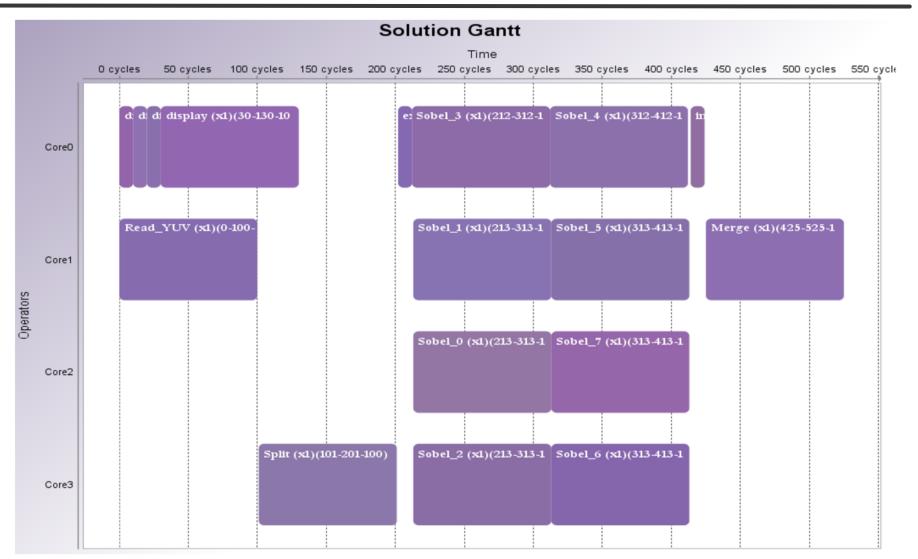

# **Actors scheduled**

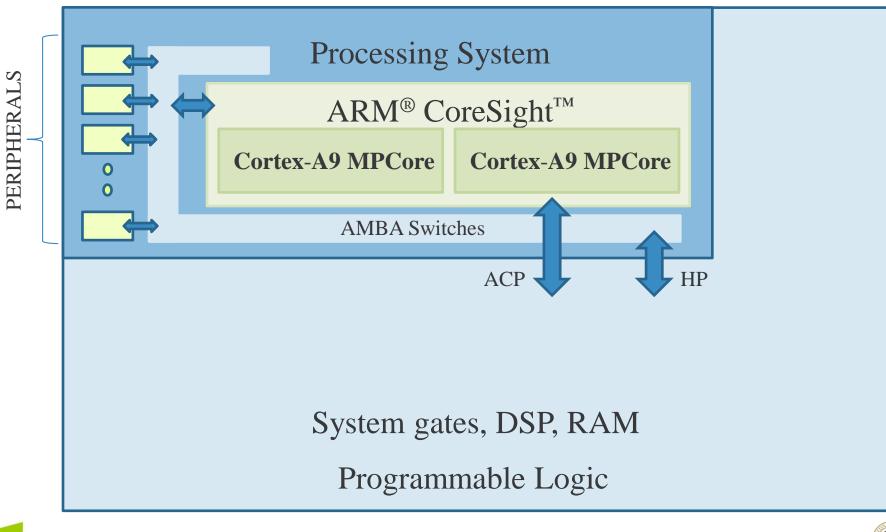

# **Heterogeneous System**

#### Zynq-7000 family

ReCoSoC

11

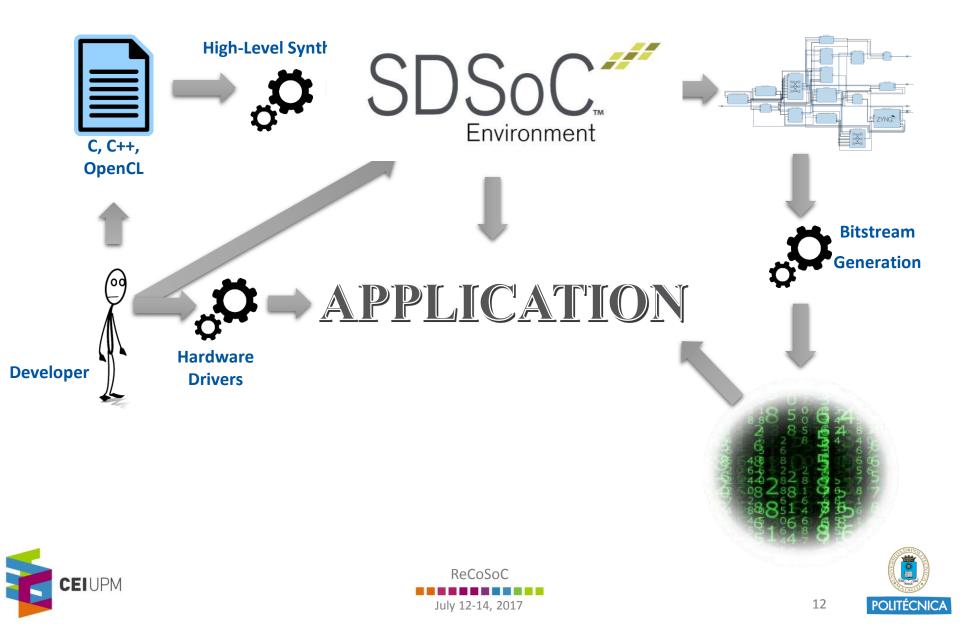

# **High Level Synthesis and SDSoC**

# From PREESM to SDSoC

## **Results**

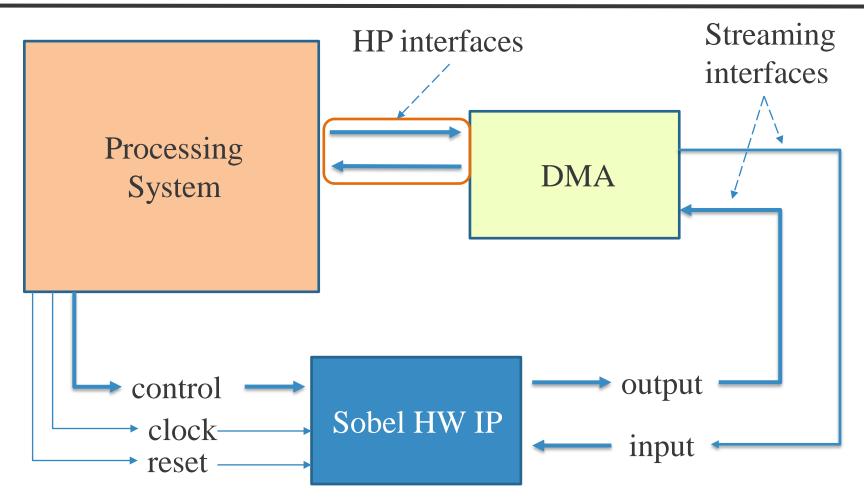

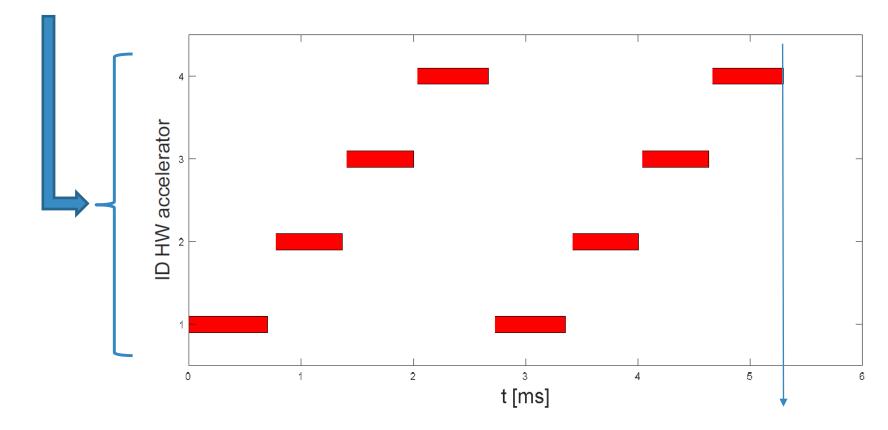

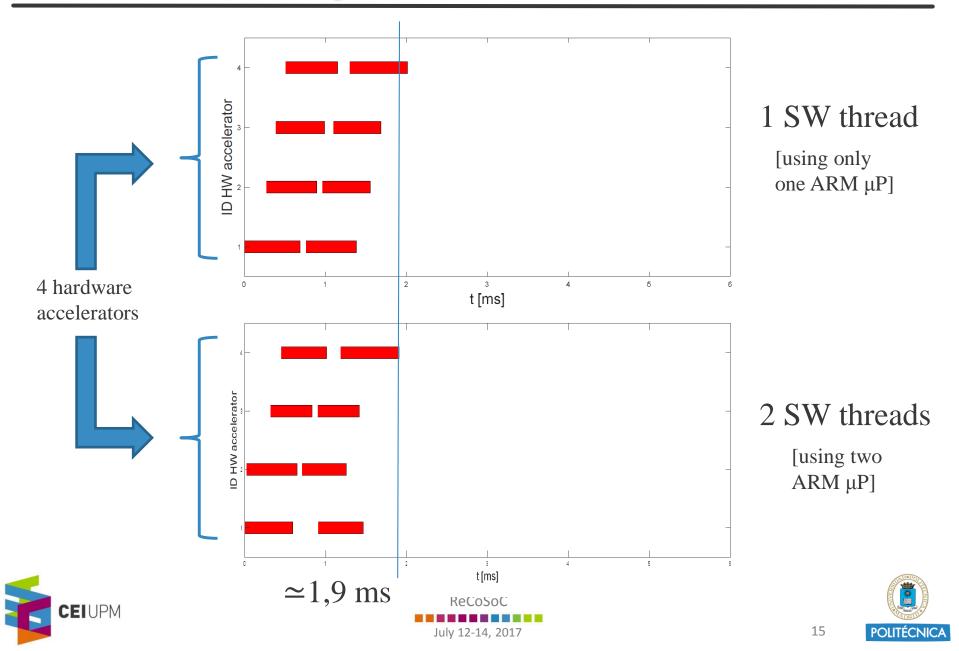

#### 4 hardware accelerators

≃5,25 ms

## **Asynchronous calls**

## **Results**

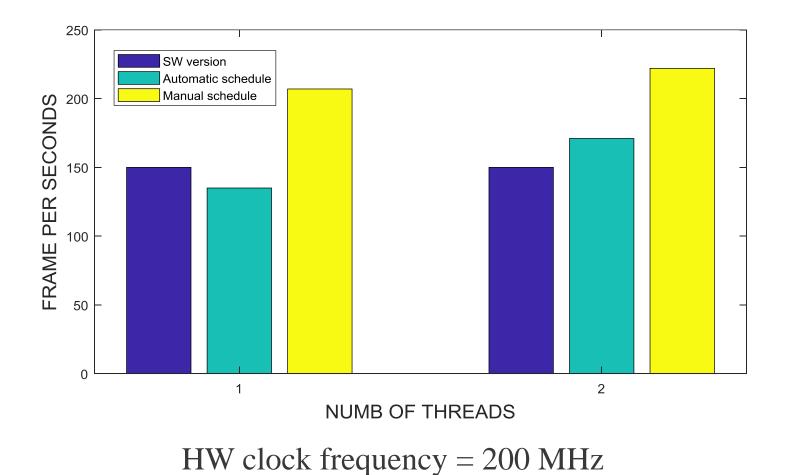

| 1 THREAD – 8 SLICES – 4 ACCELERATORS |         |         |         |  |

|--------------------------------------|---------|---------|---------|--|

| HW freq.<br>[MHz]                    | 142.86  | 166.67  | 200     |  |

| SDSoC HW<br>handling                 | 115 fps | 125 fps | 135 fps |  |

| Manual<br>handling                   | 200 fps | 205 fps | 207 fps |  |

| 2 THREAD – 8 SLICES – 4 ACCELERATORS |         |         |         |  |

|--------------------------------------|---------|---------|---------|--|

| HW freq.<br>[MHz]                    | 142.86  | 166.67  | 200     |  |

| SDSoC HW<br>handling                 | 150 fps | 160 fps | 171 fps |  |

| Manual<br>handling                   | 211 fps | 218 fps | 222 fps |  |

ReCoSoC

July 12-14, 2017

# Comparison

ReCoSoC

# **Conclusion and future work**

Integration of existing tools for deadlock-free code generation and hardware acceleration

Manual strategy of hardware calls can improve performance by asynchronous hardware invocations

PREESM evolution:

automatic generation of code for hardware generation

Integration with ARTICo3 for parallel processing speed up, flexibility, resource multiplexing in time, fault tolerance, energy efficient execution

done

on going

# Thank you for your attention

ReCoSoC

July 12-14, 2017